Tool/software:

Dear Team,

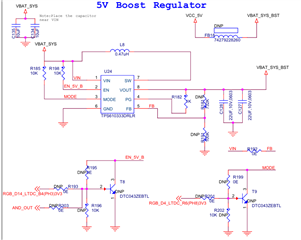

Attached is the schematic for TPS610333DRLR regulator.

We have done 2 test cases with this Boost regulator

1.With mode pull up option provided - Observed more(increase of 6mA) current in sleep mode

2.With mode pull up option removed - Observed reduced current(reduced by 6mA) in sleep mode (Mode pin is left floating)

A) Let me know whether we can keep mode pin as floating is it feasible for the design? What is your feed back on it.

B) Or is there any approach from your end to reduce the current of boost in sleep mode condition.