Other Parts Discussed in Thread: TPS82130, TPSM82866

Tool/software:

Hello,

we are facing noise pickup on a new prototype board featuring several TI step-down switchers.

We must generate several voltages in the 1V0 ... 3V3 range that "gather" underneath an FPGA (core voltage, aux voltage, several I/O bank voltages).

The board features 3 TPSM82864 and 2 TPS82130. All are using the same 5V VIN. The TPSMs are running in forced PWM mode (with external FB divider).

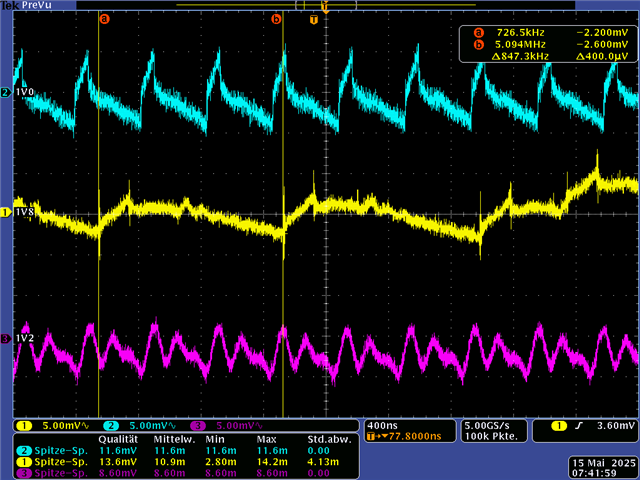

We (seem to) have evaluated that much, that the (internal) switching of the TPSMs is "generating" the noise that is seen on the TPS82130 output voltages. The TPSM output voltages seem to be fine (just normal ripple in the range 10mVpp, no pickup noise here).

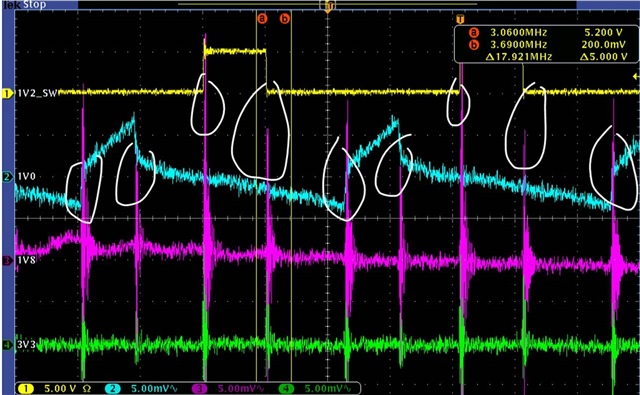

The TPS82130 output voltage (5V VIN, 1.8V VOUT) shows the expected ripple (in frequency and p-p voltage), overlayed by 120mVpp pickup noise "peaks" (noise is rather wide in spectrum, around 500MHz). We have "pinned" the noise peaks to the switching moments of the 3 (free running) TPSMs (scope shot). Looking at the TPSM SW pin, this one is generating really fast switching edges.

The noise is already present at the TPS82130 VIN (5V), so it may be that the noise that has initially been detected at the TPS82130 output (we are having micro-coax connectors on our onboard output voltages that connect via 50R + u-coax/SMA-50R-cable to the BNC connector on the scope 1Meg input) is just passed through by the TPS82130 (and so becomes visible at its output). The noise is not present (or at least not measured that high) in the area were the 5V source enters the board). So it seems the 5V = VIN noise is generated on board at the times the TPSMs are switching.

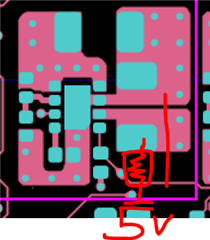

Layer stack is L1 (Top), L2 (GND), L3 (Signal), L4 (Signal), L5 (GND), L6 (Split Power 5V0 = VIN, 1V0, 1V2, 2V5), L7 (Split Power 1V8, 3V3), L8 (GND), L9 (Signal), L10 (Signal), L11 (GND), L12 (Bottom).

TPSMs: CIN 22uF, COUT 2x 22uF. TPS82130: CIN 22uF, COUT 22uF.

Any ideas were to look at? We seem to know who is "initiating" the noise, but what happens exactly? What can be improved in the layout? Should we have added some 1..10nF caps to the TPSM or TPS inputs? Can anything be done at the SW pin (snubber etc.)?

Thanks,