Tool/software:

Hi ,

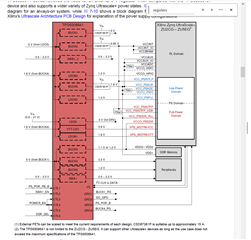

when TPS6508641 power off, I need to keep POWER EN low level, then the FPGA powe down, how can I assure the POWER EN keep low during the FPGA power off?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

For TPS6508641 CTL4 initiates the power down sequence and it should be coming from external. How is it configured on the board (for power up)?

Sathish

Hi,

How are you making the TPS6508641 power off?

If you drvive POWER_EN pin low then TPS6508641 will power off, this is an external driven pin.

Sathish

Hi,

The block diagram in the datasheet shows always on power map example, so you could directly connect it to LDO3P3 without any pull up.

Sathish

Hi,

After VIN is removed from TPS6508641, LDO3P3 will go low and this will take CTL4 (connected to LDO3P3) (POWER_EN) low.

Hi,

I can help provide support while Sathish is out of office.

POWER_EN (CTL4) depends on your system's design and desired enable control.

External MCU is not necessary, typically POWER_EN can be connected to a push button circuit, supply power good, or any other method of enabling/disabling the power.

What is the desired method of initiating power-down sequence, with an external push-button signal, I2C signal, or power good monitoring?

This can help identify the best connection method.

Best Regards,

Sarah