Tool/software:

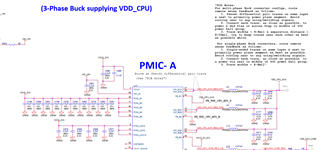

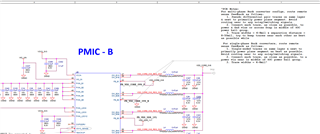

We have chosen the TITPS65941213+TPS65941111 power supply solution, and the following issues arise:

1. If we design according to the power supply scheme provided in the document "PROC112A1 (001) _SCH" on the official website, the newly purchased TPS65941213 and TPS65941111 chips do not require additional software configuration. Can each power supply directly output normally after power on; If VIN is changed to 5V input, no additional configuration is required when powered on, what is the difference between it and 3.3V input.

2. Do the sampling points FB1 and FB2 of PMIC-A and PMIC-B in the figure have to be located below SOC as given in the document, and do they have to be pseudodifferenced.