Tool/software:

Hi team,

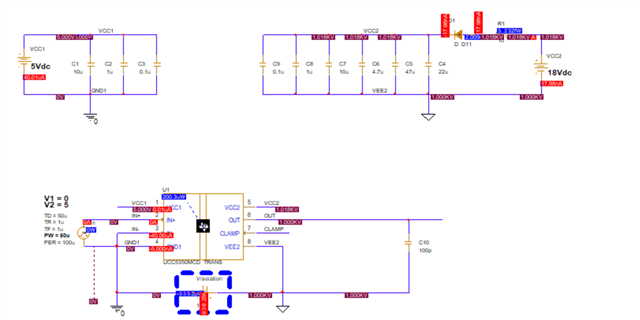

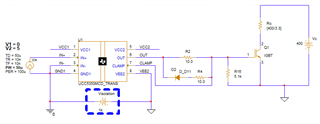

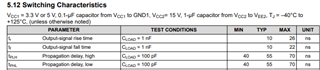

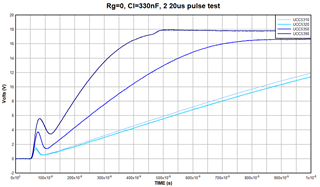

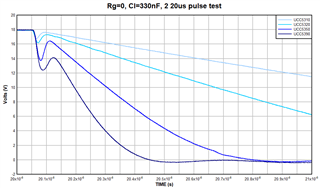

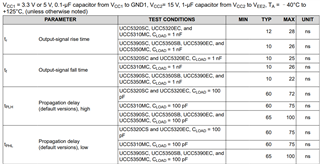

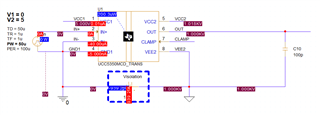

we want to evaluate the UCC5350MCDR device timing, after using the UCC5350MCD_TRANS-PSpiceFiles file to reproduce the performance on datasheet like tR 10ns ,tPLH = 65ns~100ns at 100pf load. if it works, we will add custom circuit for real result. but the PSpice simulation result seems different , can you help to check how we can get the target result here?

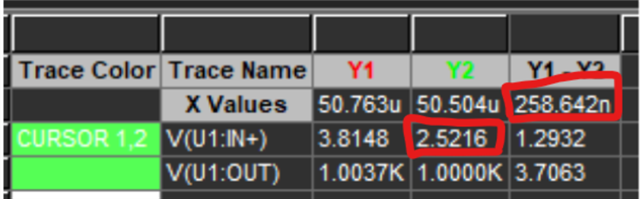

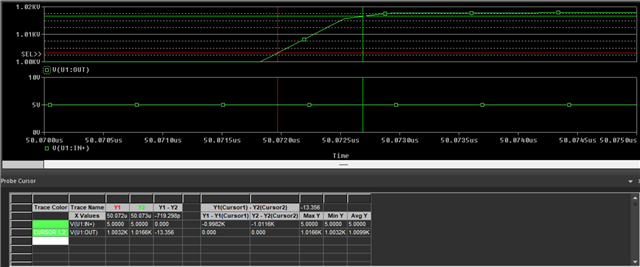

what we set now :

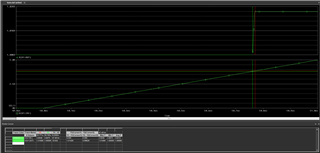

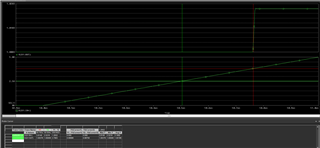

result: output as 260ns for tPLH

tR as 9.25ns is correct.