Other Parts Discussed in Thread: UCC27324

Tool/software:

Hello,

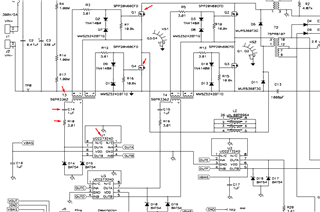

In Picture 1, I put some arrows on the UCC27324D driver, capacitor (C14), transformer (T3) and mosfets (Q1 and Q2) to follow easily on the picture. Application is phase shift full bridge dc-dc converter.

I may have a mistakes in my way of thinking but let me summarise as follows:

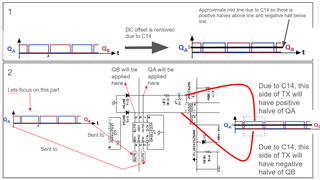

When I first look at section that I put arrows on them, I saw C14 capacitor. This capacitor reminds me it removes the DC offset from the signal coming from UCC27324D outputs (OutA, OutB). That means this capacitor will change the signals into something like VoutA-VC14 being high state and -VC14 being low state. Same thing happens to the OutB which is VoutB-VC14 being high and -VC14 being low. (Vc is the voltage on the C14 capacitor.)

UCC27324D IC is given as dual noninverting in it's datasheet which means outputs will follow inputs.

So let me come to the point which makes me very confused as follow:

We know that the input signals of UCC27324D are phase shifted signals coming from UCC28950. We also know that there is C14 capacitor. This capacitor (as I explained it's mission above) will affect the signals coming from UCC27324D in such a way that these signal will have positive half and negative half due to DC offset removal. isn't it? You can see what I mean in the picture 2. I draw an approximate mid line on the signal to show positive and negative half.

Considering these signals (DC blocking is in play), transformer will have one positive from one side (pin 1 of TX) and one negative section from the other side (PİN 2 of TX) at the same time .

Meaning that if I have let's say for simplicity +10V on the pin 1 of TX and -10V on the pin 2 of TX, is this create 20V on the transformer ? or when both of the signals is on the negative half, meaning 0 V across the transformer . Is this how these signals (considering the effect of DC blocking capacitor) work on the transformer ?

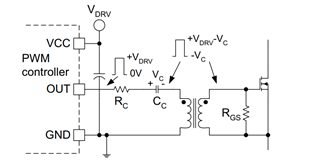

Picture 1. The circuit given in the datasheet

Picture 2. The explanation of what I tried to say in the question

Picture 3. To emphasize what is the effect of C14 capacitor