Other Parts Discussed in Thread: CSD95490Q5MC,

Tool/software:

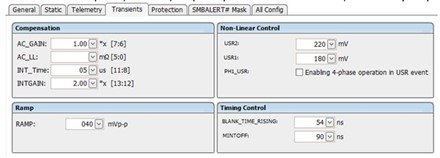

Now I am using TPS53679RSB and CSD95490Q5MC to build two channels output VRMs (12V input, channel A 2phase for 0.9V/65A output + channel B 2phase for 3.3V/40A output). In the application, SVID and DC load line are disabled. And under controller TPS53679 phase, inductor, output capacitors (especial for all ceramic output capacitors) are determined, is there any simple method to compute digital compensation parameters (AC_GAIN, AC_LL, INT_Time, INTGAIN and even RAMP, etc) illustated below to ensure power supply stability (loop phase margin), for example with some formula, excel or GUI auto tune functions? For all ceramic output capacitors, what should I pay attention to? And could you give some advice?

In additon, I would like to simulation the VRMs described above, and how to simulate it, could you give some recommends? And how to adjust the digital loop (parameters)? Could you supply the devices (TPS53679RSB and CSD95490Q5MC) model? And how to change digital compensation parameters in simulation tool, for example in PSpice tool?