Tool/software:

I've been studying a SEPIC with reports of frequent failures. The final failure scenario is a short between SW and PGND.

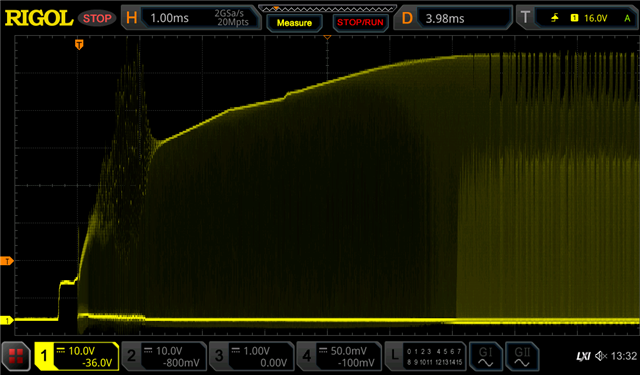

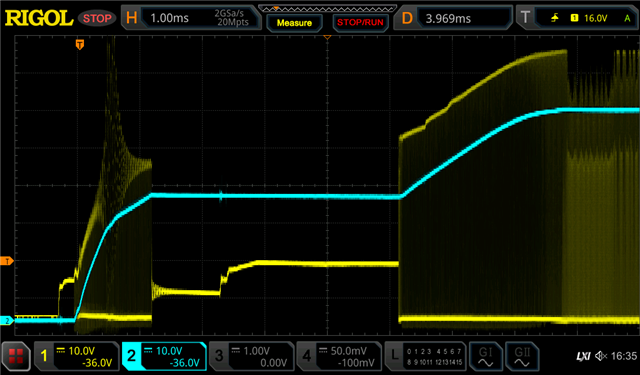

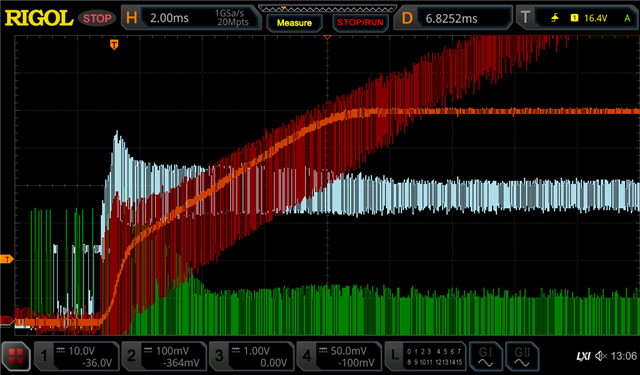

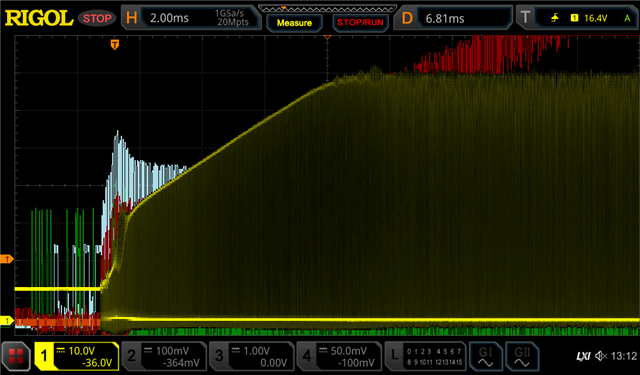

I've confirmed the part choices satisfy the Excel design tool, and in steady state the operation looks good. But I've noticed on some boards there is a repeatable, large oscillation during the soft start.

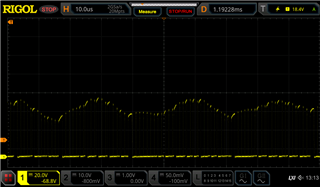

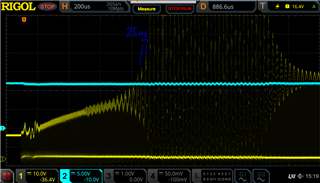

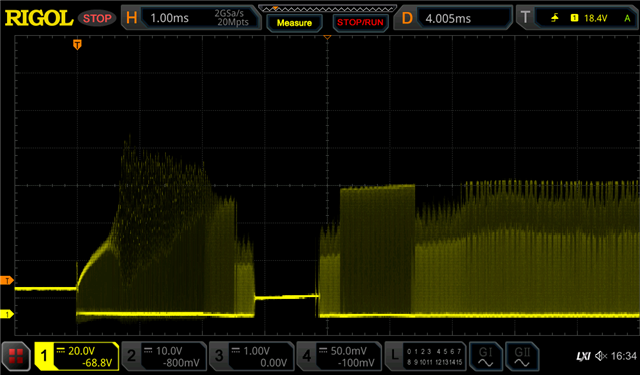

In this case the switching stops and resumes a short time later, everything apparently happy again. The stop period is not always present, but the oscillations are. Here's the start of the oscillation:

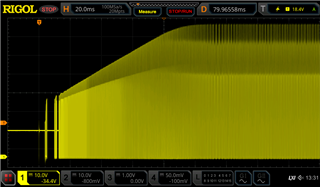

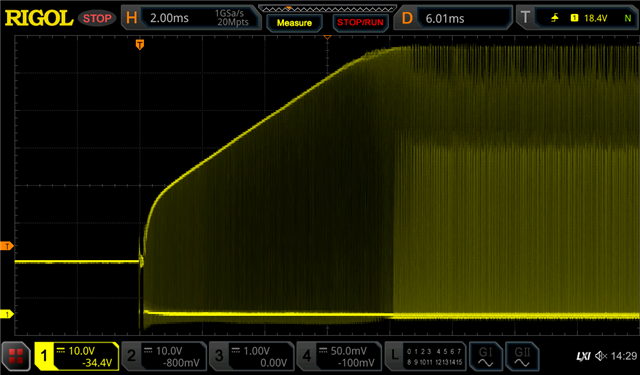

For comparison, here's a "good" (to me) startup, from the same circuit, same layout, but a different part of the board:

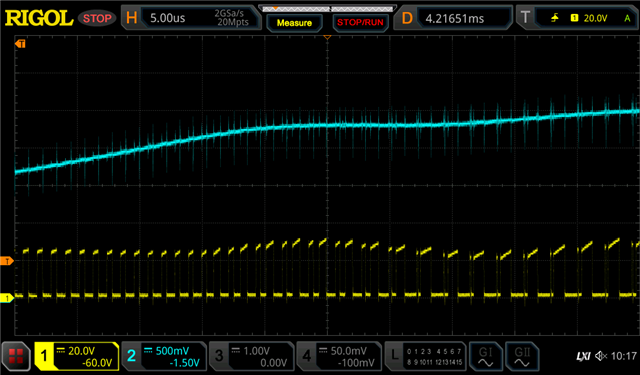

The input voltage is 14V and steady. I'm holding the LM5158's EN low and then releasing it when I'm ready to capture the start up event.

The output voltage is 56V. There is no load on it, apart from an idle LTC4263 and its decoupling caps. Although, the input current still rises by 36mA once at steady state. The converter is designed for a 200mA output current.

The switching frequency is set to 915kHz and is effective. During the oscillations I can see the switching duty start varying wildly.

The soft start is set to 10ms, although always seem to start faster than that - between 5ms and 8ms.

Recall that the LM5158's cycle-by-cycle current limit is 3.26A. The inductor's saturation current is 8A.

The max SW voltage is 83V, which is not exceeded in normal operation (14V+56V=70V) but is during these oscillations.

The oscillation frequency is a bit less than 10kHz.

I guess some noise is getting into the feedback loop but the SEPIC characteristics are so complicated I'm having trouble narrowing down potential culprits. I'm wondering:

- Is this a known phenomena?

- What could be resonating at this frequency? A slightly higher input capacitance and the input inductor? But the switch breaks the loop every cycle. A lower output capacitance and the output inductor? But the diode would have to have meaningful reverse conduction?

- With a compensation loop bandwidth of 4.15kHz, should it be attenuating this oscillation and therefore is not working?

- Does this look like it could be caused by bad control, or is there something more significant going on?