Other Parts Discussed in Thread: TPS62088, TPS628503, TPS628511, TPS628513, TPS628501

Tool/software:

Hi expert,

Customer is looking into some of our power sequencing and have a question regarding the Logic Interface EN on two specific power supplies:

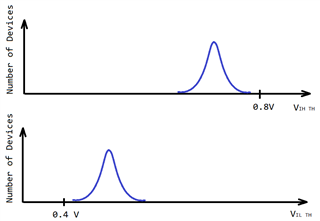

- TPS62801 → VINH TH = .8V, VINL TH = .4V

- TPS62088 → VINH TH = 1V, VINL TH = .4V

What we currently do not understand is if there is hysteresis/ a Schmitt trigger on these pins. For context, we are using an RC filter to provide the appropriate power sequencing that we will need. It will take over a ms with our RC network for the Enable pin to go from .4V (Logic low) to .8V (Logic High), but if there's not hysteresis or a Schmitt trigger and the pins operate like a digital IO, we may be inadvertently enabling one of the devices over a millisecond before we intended to.

Could you please clarify how we can expect these pins to behave? Also please let me know if I should submit another request for the other part # TPS62088.

Thank you!

McKenna