Other Parts Discussed in Thread: LM74930Q1EVM, LM74930

Tool/software:

In a design with considerable output capacitance (3750 uF, bulk capacitance for motor drivers), the circuit fails to bring up the output voltage if the input capacitance isn't sufficiently large compared to the output capacitance.

The nFLT pin is then pulled low signalling a fault condition.

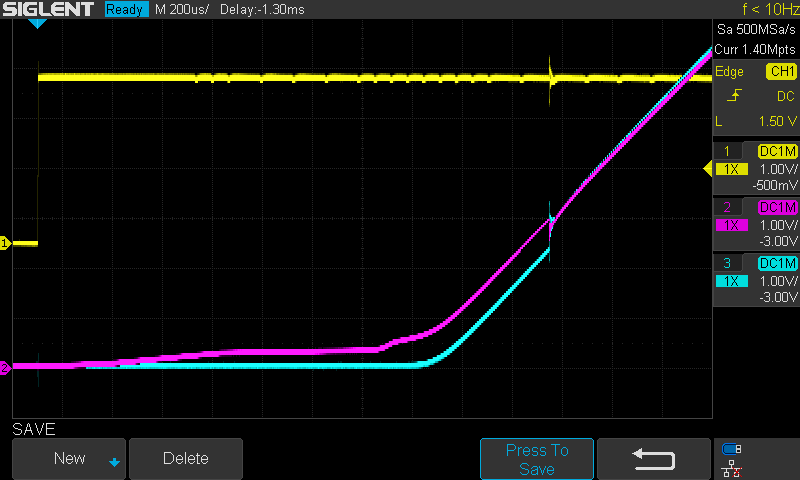

After some investigation it appears that this is triggered when V_A (common source voltage) reaches the V_A_PORR threshold and DGATE is enabled.

Up to this point the ideal diode MOSFET is conducting through the body diode and hence has a diode voltage drop across.

The effect of the ideal diode MOSFET suddenly turning on without sufficient input capacitance is that instead of pulling up the output voltage it actually pulls down the V_A voltage, dropping below V_A_PORF again and disabling the MOSFET.

At this point HGATE stops rising as well. I don't understand exactly why.

If the input capacitance is too low, it never actually manages to complete the soft start ramp and Vout never rises above V_A_PORR minus a diode drop.

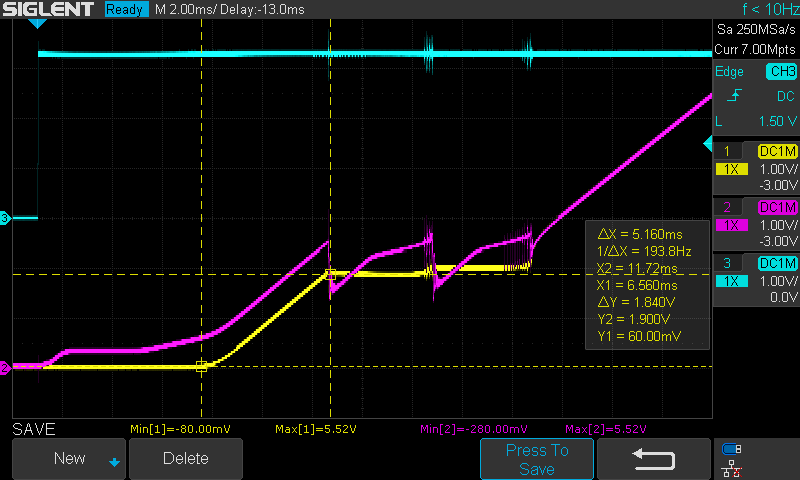

If the capacitance ratio Cin/Cout is close to the limit, then it can oscillate around the V_A_POR thresholds a few times, eventually managing to get past the V_A_POR thresholds, and at this point Vout starts rising again with the expected slew rate. Afterwards everything operates normally.

If Cin is much larger than Cout, on the other hand, the startup is clean every time and Vout always rises as expected with the correct soft start delay.

This behavior was reproduced with the LM74930Q1EVM evaluation board.

Is this a known issue? Are there any mitigation measures I can implement to reduce this problem?

This is very annoying since one of the duties of the LM74930 in the system was precisely to function as inrush current limiter for the large capacitance.

Thanks in advance

Damiano