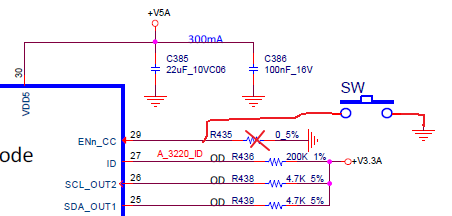

Tool/software:

Hi, Sir,

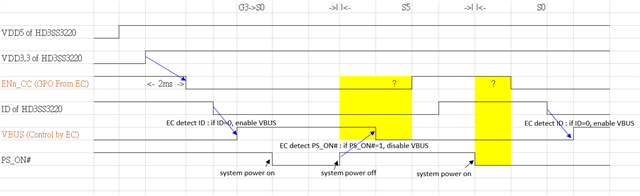

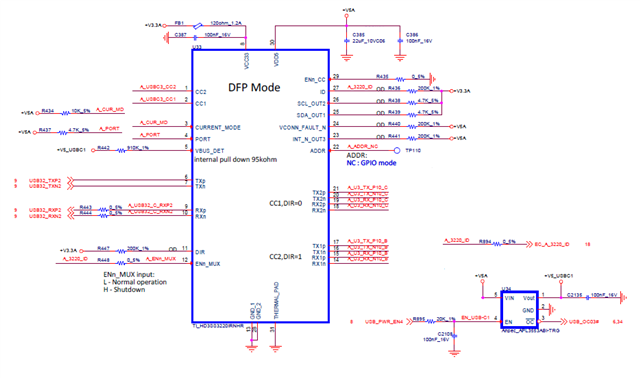

We have a motherboard design that uses the HD3SS3220 for the USB Type-C port, and the schematic is as below:

To save power, the system disables the VBUS power after the OS enters shutdown.

However, we encountered a problem where USB3 functionality becomes unavailable after the system powers on again.

It seems the USB3 failure is related to the lack of CC re-negotiation after VBUS is re-applied.

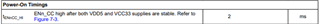

We conducted an experiment where re-enabling the ENn_CC (pin 29) signal resolved the USB3 issue. Therefore, we are considering using a GPIO to control ENn_CC.

However, the datasheet does not provide detailed timing requirements or behavior for ENn_CC control. We are concerned that improper ENn_CC control may introduce side effects.

Could you please provide timing guidelines or recommendations for controlling ENn_CC via EC to ensure proper re-enablement without causing issues?

Below is actions of our re-enable experiment using a button connected pin 29 and GND:

Step 1: When the system shuts down, the EC disables the load switch and VBUS = 0 V.

At this point, the button is not pressed, so ENn_CC is floating.

Step 2: When the system powers on, the button is pressed, pulling ENn_CC low.

This enables ENn_CC, and pin 27 (ID) is pulled low.

The EC detects ID = 0 and turns on the load switch, restoring VBUS to 5 V.