Other Parts Discussed in Thread: LM25184-Q1

Tool/software:

Hi,

i'm trying the evaluation board LM25184EVM-S12, with default configuration and it's ok, very good results.

24V In, 12.33V Out, 125 mA

Than I increased soft start capacitor from 47 nF to 470 nF and Vout regulation was not stable over the time, changing of tens of millivolt.

So I mounted a reasonable value of 100 nF and for a good period of time the Vout was stable.

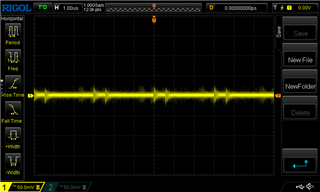

Today, in the same conditions, the board worked good for a while, then was not able to keep regulation with same load, the output voltage dramatically changes over the time, reducing until 0 V after few seconds.

So I mounted again a 47 nF soft start capacitor and now the Vout is stable.

I can't understand the correlation between soft start capacitor and Vout regulation. Am I missing something?

Thanks