Tool/software:

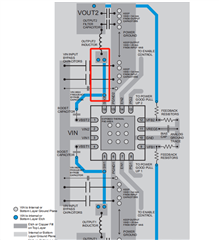

Hi,i have an issue about the layout in the datasheet at 16-17 page,the SW pin of the ic connect to the inductance, that isn't in top layer,but in inner layer,why do it? I observed other DC-DC chips where the SW pins and inductor wiring are on the same layer,so I'm confused.