Other Parts Discussed in Thread: C2000WARE, SFRA, SYSCONFIG

Tool/software:

Hi,

We're working with the TIDM-02013 reference design, trying to use it as a baseline for an EV charging product.

For the validation process, we are using the board's reference documentation, which is available on the website.

We succeeded in validating the CLLLC stage, but are having problems validating the PFC stage.

We are following the procedures outlined in the document.

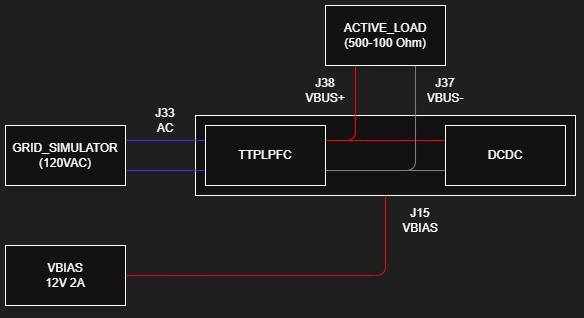

This is our test setup:

# ISSUE1 - The simulated plant for the PFC is not included in the project

In Lab 2, a graph shows how a simulated plant is used to compute the initial current controller. However, in the C2000Ware_DigitalPower_SDK_5_05_01_00 project, there is no syscfg file, so we cannot use any simulated plant.

We tried the compensator that was specified in the documentation.

K=0.35, Fz=0.03kHz

However, the system triggers an overcurrent trip when the inrush current relay (lab2, current loop DC) is closed with an input voltage of 50 V and a load of 500 Ω is connected.

Capture here (CH1:pwm, CH2:dc_link, CH3:current, CH4:dc_in):

We tested several controllers and achieved stability with the following:

K=0.1, Fz=0.03kHz

Questions:

- Is this approach acceptable?

- Are we missing something in the DigitalPower SDK that could enable us to compute this controller?

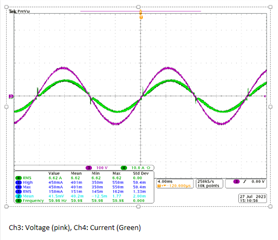

# ISSUE2 - Current instability in high-load scenarios

Using the controller obtained in the previous case, we managed to complete the remaining laboratories (lab2, lab3 and lab4) with a low load. However, when we increased the load to 100 Ohms, the current became erratic and the system triggered an overcurrent protection after a while.

Below are some captures using different loads:

R300 – OK.

R200 – Start current issues.

R150: some spikes in current.

R100: extreme current swings.

Questions:

- Could this behaviour be caused by the chosen current controller?

- If so, how can we design a solution for our board?