Other Parts Discussed in Thread: UCD90SEQ64EVM-650, UCD90160

Tool/software:

Dear Team,

We are using the UCD90160ARGCT power sequencer in our design, and we are validating it with TI Evaluation Kit (UCD90SEQ64EVM-650).

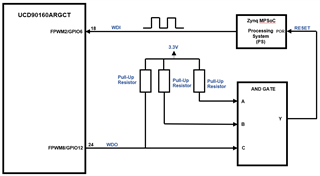

Below attached is the Block diagram of the Watchdog circuit used in our design:

GPIO6 is configured as the watchdog input and GPIO12 as the watchdog output.

A periodic pulse is given from Zynq MPSoC to GPIO6 of UCD90160ARGCT (Watchdog Input).

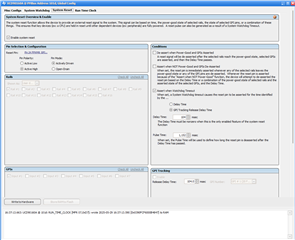

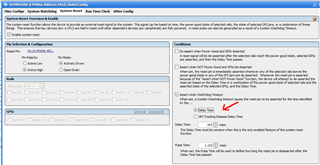

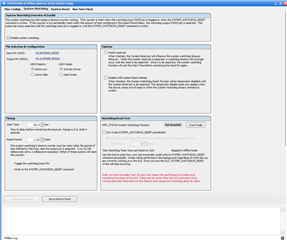

Additionally attached the Screenshot of the configuration in GUI

We observed the following behaviour:

When the watchdog input (GPIO6) is pulsed periodically, the watchdog output (GPIO12) remains high, as expected.

When the input pulse stops, the watchdog output goes low — also as expected.

However, our requirement is for the watchdog output to go low when the input pulse stops, and then automatically return to high. Currently, the output remains low and does not return high until we manually intervene.

Could you please confirm:

- Whether the UCD90160 supports this type of watchdog output reset behaviour?

- If so, how can it be configured (via GUI or registers)?

We would appreciate your guidance on how to achieve the desired watchdog behaviour.