Tool/software:

Hi Ti experts,

My customer uses TPS274C65AS in PLC IO module. They met some issues and have five questions:

Q1: After power-on, 0h register is 0x81 or 0xC1, which means there is a UVLO case. Is it normal. Is there a actual UVLO case.

What operations should customer do on registers after POR. Customer didn't use NMOS for RCB. I know customer should set 23h bit7 RCB_DIS to 1. Anything alse?

Q2: After power-on, 0x register's value is not same as customer's expectation. Customer read once all the registers and 0h register back to 0x00. Is the reason that 2h register's type is RC and it will reset 0h register after once read operation.

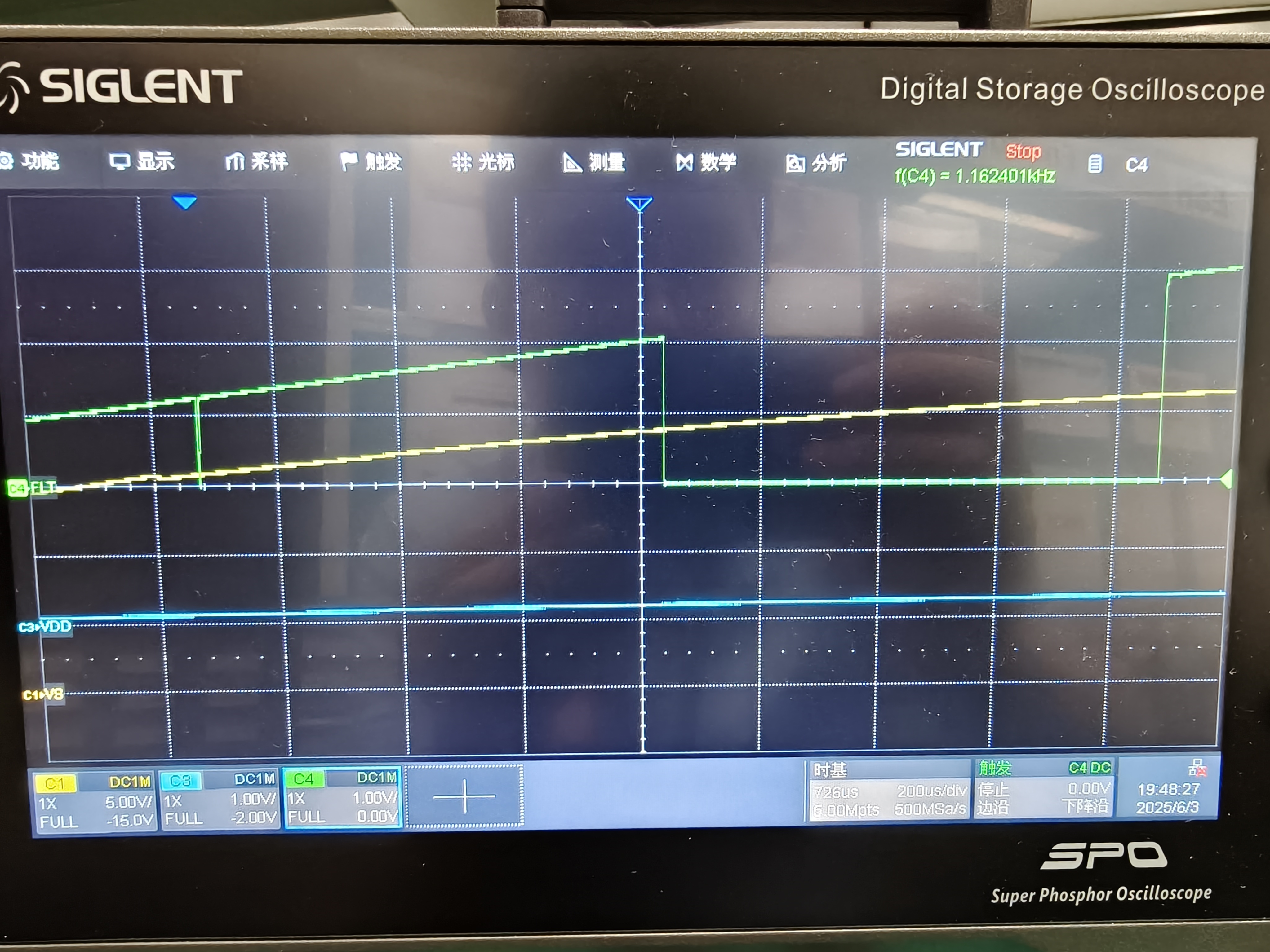

Q3: Fault signal will have twice drops when POR. Is it normal?

Yellow is Fault signal and green is VDD from IC internal LDO rather than external DCDC.

Q4: Output voltage, input voltage and fault will have output oscillations when normally working. This is a mandatory malfunction.

Yellow is fault. Blue is VS. Green is output. You can see each time when the ouput opens, there will be a oscillation.

Q5: After POR, Customer only operates 1Dh register. Fault will have a drop sometimes but output voltage will not drop at the same time. But after customer read once all the registers. The issue will not happen.

Yellow is fault signal(Green is on the MCU side after optical coupler). Red signal is the output voltage. Blue signal is the

You can see output voltage didn't drop though fault drops.

\

\