Tool/software:

Hello,

I am bringing up a design with a dozen TPS1HTC30-Q1s as high-side load switches. The parts are exhibiting behavior that doesn't match the datasheet and I'm hoping for some input on what might be going on.

All the instances on my board behave the same way, so it's not an issue of one damaged part. The PCBA is also straight from the assembler and has only been handled in an ESD-safe environment. I also confirmed the pinout was correct, the part markings match the datasheet, component orientation is correct, and there are no short circuits.

My test configuration is as follows:

- 28 V supply

- EN pulled low by microcontroller via 10k series resistor

- 24.9k on ILIM pin (for a 4 A setpoint)

- 768R on SNS pin

- LATCH tied to GND

- DIAG_EN tied to 3.3 V

- 100k pull-up on nFAULT

- No load attached (to start with)

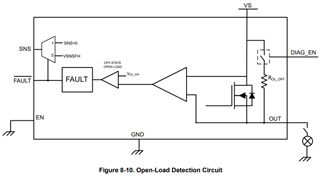

When I first powered up the PCBA, I noticed with a thermal camera that all the TPS parts were heating up by about 10ºC above ambient. When investigating further, I measured that the VOUT pins were 330 mV HIGHER (!!!) than my supply voltage. nFAULT was pulled low, consistent with open-load detection, but the SNS pin read 3.47 V, which indicates a roughly 6 A current sense reading. (Again there is no load present, and the total current into the board is much less than 1 A.). That SNS voltage also should not be possible since the datasheet indicates it will not exceed DIAG_EN voltage of 3.3 V.

When I connect a 22R load resistor to the output, the part appears to behave normally. The heating stops, and the current draw from my 28 V supply drops by about 7 mA. SNS pin now reads 0, and nFAULT is deasserted.

My design has no boost converters or charge pumps besides the ones in the TPS1HTC30s for the internal gate drivers. My hypothesis is that somehow the charge pump output is making its way to the VOUT pins and passing through the body diode of the internal MOSFET, but based on the simple internal block diagram and all the information available in the datasheet that really shouldn't be possible.

I will continue investigating - including seeing what happens when I assert EN high (need to make some firmware changes before I can do that) - but wanted to put this out there now in case anyone has seen anything similar.

Thanks!