Other Parts Discussed in Thread: LP87524J-Q1

Tool/software:

Hello,

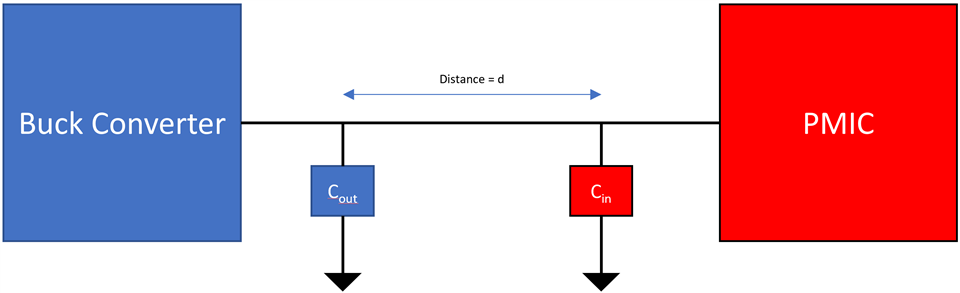

I have a question regarding the output capacitor configuration for the LM60430-Q1.

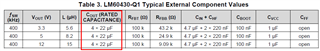

According to the datasheet, the recommended output capacitor configuration consists of four 22uF capacitors. We understand that this recommendation is intended to ensure stable operation under the maximum load current of 3A.

In our application, however, the maximum current required from the LM60430-Q1 is only around 720mA to 1A. Therefore, we are considering reducing the output capacitance to two 22uF capacitors.

Could you please confirm whether this configuration would still be acceptable for our lower current requirement? We would appreciate your guidance on this.

Thank you.