Tool/software:

Hi,

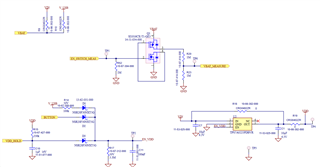

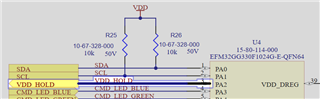

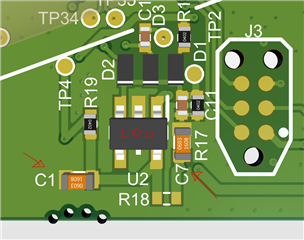

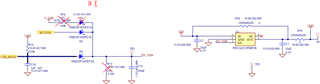

I encountered problems with the TPS7A0225PDBVR on our PCBs. It looks like the EN pin is making the LDO shutting down because when I bypass the LDO, the PCB works fine. Apparently in the datasheet if this pin is in floating state the LDO is shutting down. I'm pretty sure this problem is occuring but I don't understand why. Is this component sensitive to EMC/vibrations problems ?

The power on working is simple, first, you push the button S1 and then the MCU sends 1.33V on the VDD_HOLD pin. You can find the schematics for better understanding.

If you could help me understanding the behaviour of the TPS7A0225PDBVR I would be more than grateful. Thanks

Regards,

Leo