Other Parts Discussed in Thread: CD40194B

Tool/software:

Dear team,

My customers want to use TPS48111-Q1 without MCU control.

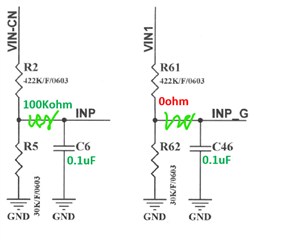

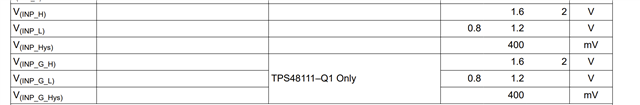

they tied the EN/UVLO and INPG/ INP to the VS pin 48V over resistor dividers. in this case, the INP and INP_G were pulled up almost synchronously.

now their control sequence want to pull up the INP_G first and then the INP to decrease the inrush current.

how does BU site recommend for the this non-MCU based additional circuit?

is cd40194b suitable here?

Best regards,

Hank Lin