Other Parts Discussed in Thread: TINA-TI

Tool/software:

Hi sir,

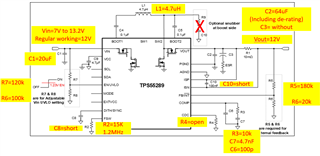

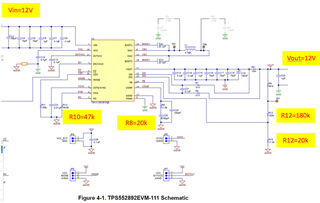

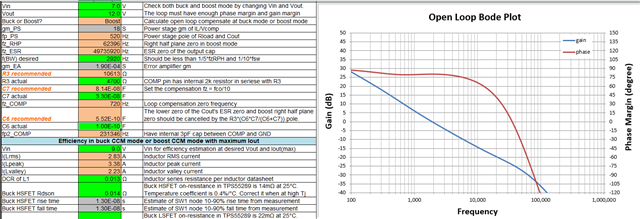

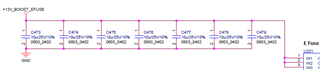

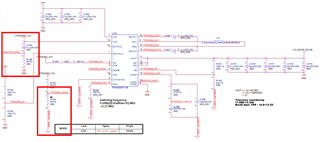

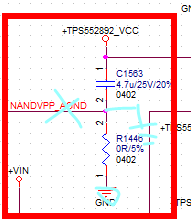

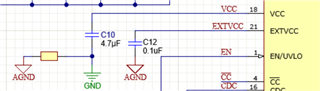

I selected TPS552892 to implement a buck-boost power supply.

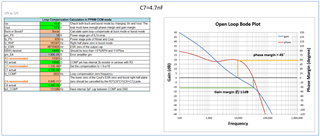

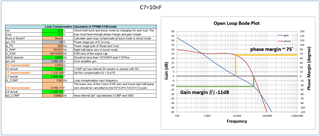

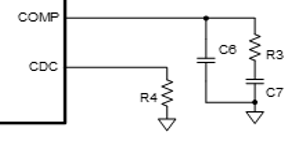

Base on the excel design sheet from TI official website, I have designed a set of parameters.

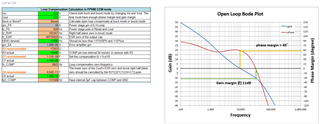

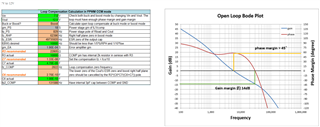

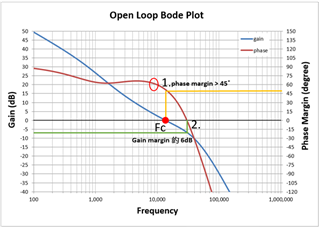

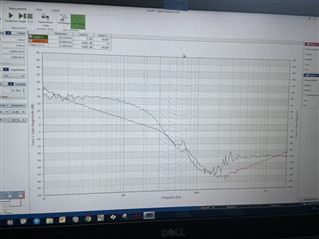

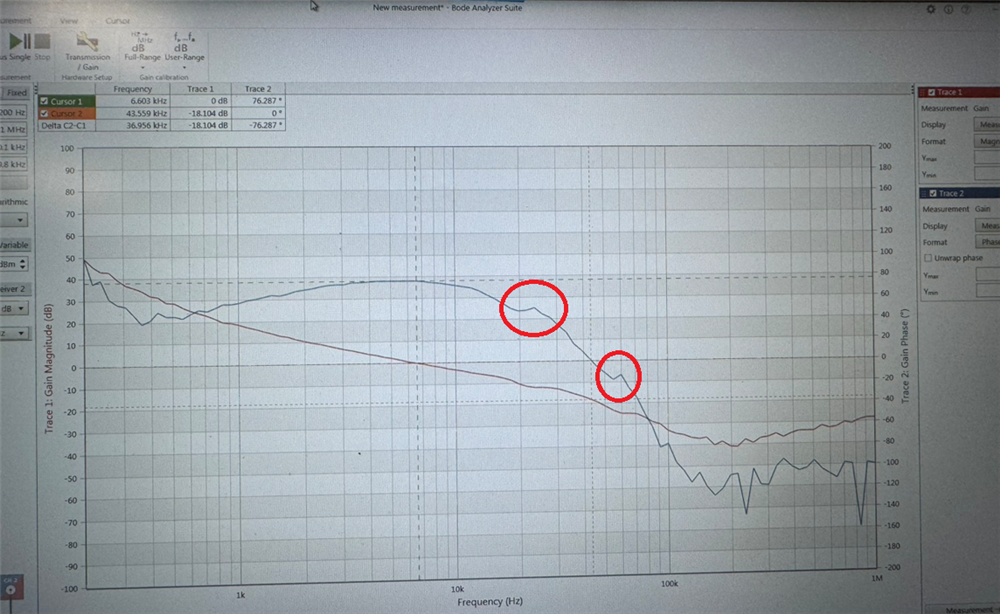

Could you please help check if there are any issues,especially regrading the feedback response stability?

The bode plot is attached for your review and reference.

Thank you !!

Parameters:

Fsw=1.2MHz

Vin range 7V to 13.2V

Vout = 12V

delta Iout=100mA to 2A