Other Parts Discussed in Thread: TPS1210-Q1,

Tool/software:

Hi expert,

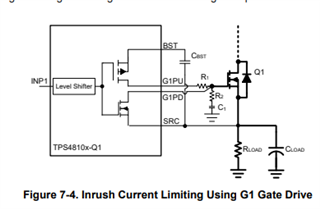

My customer (CosMX) is designing TPS4810-Q1 schematic and want to know how to design the soft start of TPS4810-Q1/ TPS1210-Q1. Could you share some principle information or reference design? Thanks.

Best Regard,

Ryker