Tool/software:

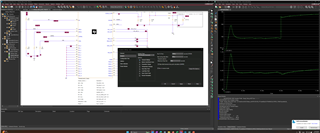

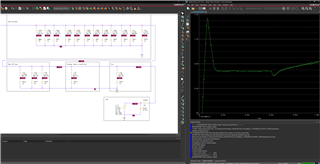

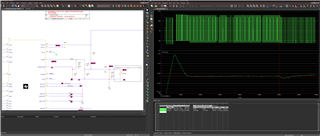

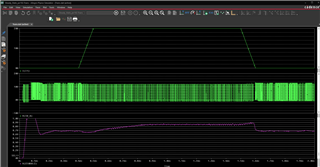

I am working on building a load model of the TPSM8S6C24MOY part. It is in use in our products. The spice model works well as given by TI. but when I modify it to match our actual schematic ( which was built in collaboration with TI and works well) I see some rather interesting behavior. In pinstrap mode, the set voltage seems to drift? Here are 3 pictures all with the same exact setup, except for the time to sim changed. The drift after the current pulse is also quite odd. I am working with a Cadence apps engineer as well to see if the tool is the problem.