Tool/software:

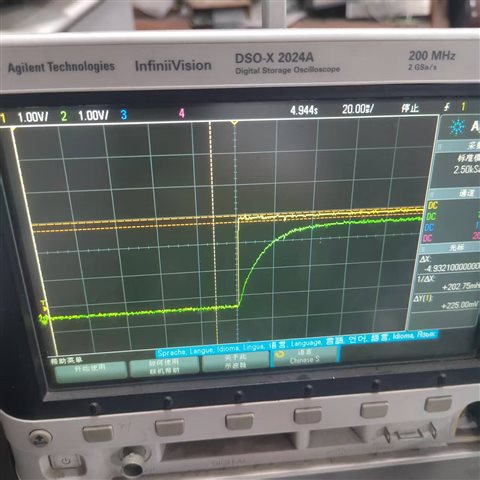

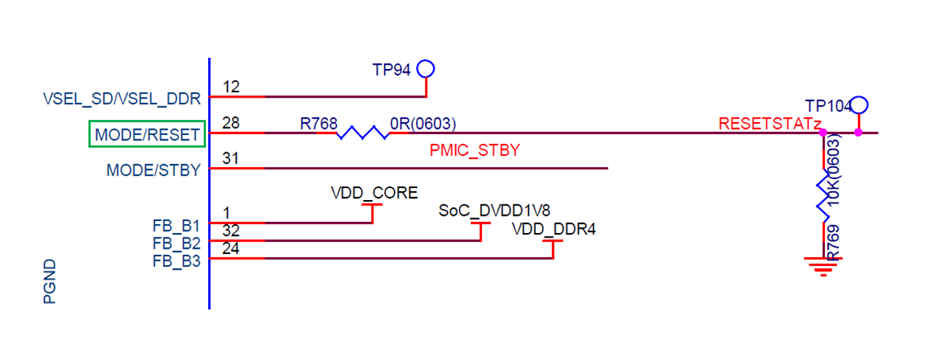

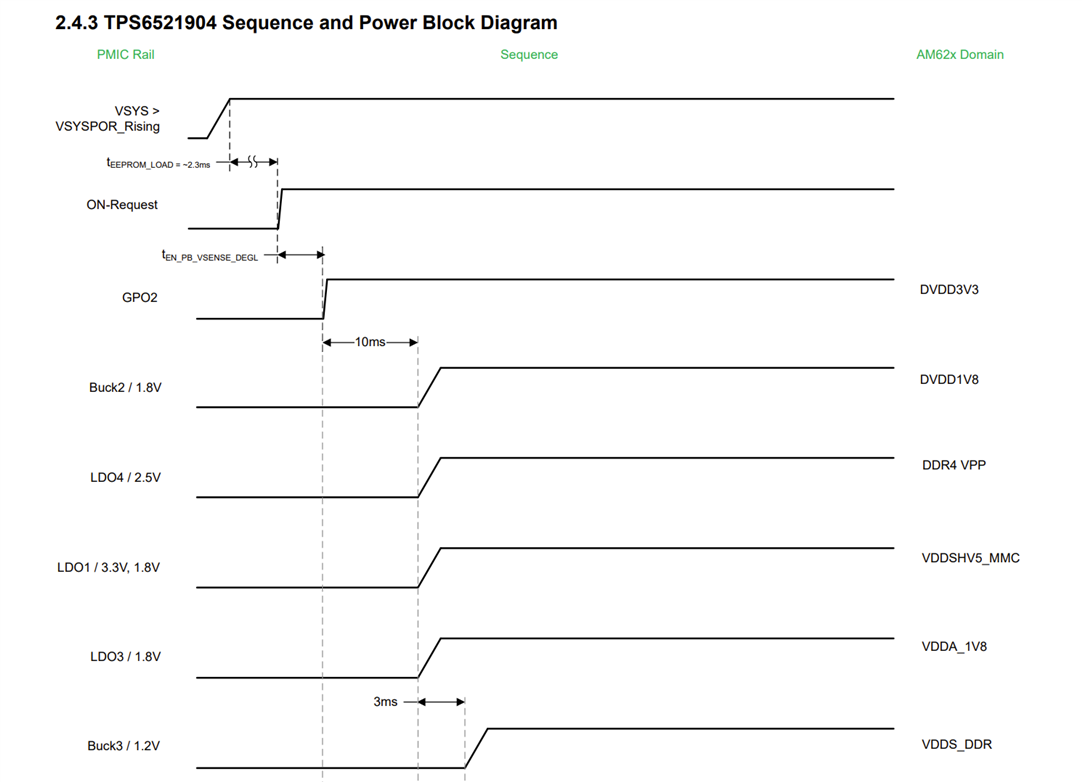

In the AM6254 core board reference. After the TPS6521901 is powered on, there is no voltage output. I need to help review the schematic diagram. Even when the TPS6521901 is changed to TPS6521904, there is still no output. thank you65219_ PAGE2(3).pdf