Other Parts Discussed in Thread: LM61495

Tool/software:

Hi, TI team:

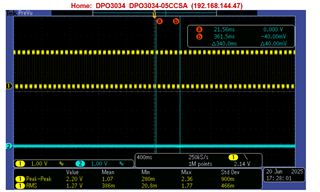

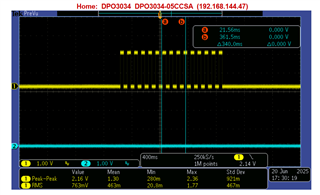

When I tested TPS6594-PMIC chip, and we found when Vbat in the 3.97V, PMIC-25 Pin( nRSTOUT ) will change 0--1.8V, but never change to 0V, please find this picture.

when Vbat in the 4.05V, PMIC-25 Pin( nRSTOUT ) will change 0<-->1.8V period, then will change to 0V, please find this picture.

Could you tell what will cause PMIC nRSTOUT pin still change, never to be 0V, and what will cause PMIC nRSTOUT pin changes sometimes, then will be 0V later? it depends PMIC output current?

because the Vbat 3.97V, current still change 0.2<-->0.4A,

when the Vbat is 4.05V, the current change 0.2<-->1.5A, then PMIC reset, current is 0.012A