Other Parts Discussed in Thread: LM5146, LM5145

Tool/software:

Hello Team,

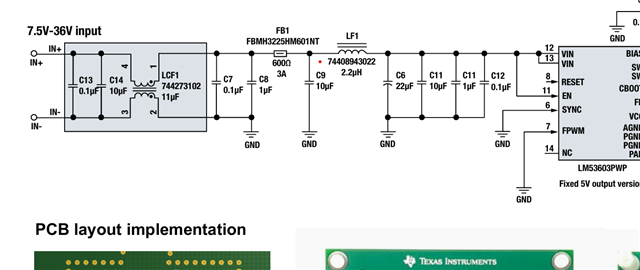

I am making a DC - DC converter. Design specifications -

Non isolated

20V - 60V input voltage (nominal - 51.2)

Output voltage - 12V

Output current requirement - 20A

Ouptut power - 240W

I came accorss LM5146ic but all the ratings and information given in the datasheet are subect to 8A and OCP is at 12A but in the quick start guide i was able to enter a value of 20A and was still withing range. So is the current limiting based on the MOSFETS ?

Also in the product details the Iout max was 20A (https://www.ti.com/product/LM5146).

Having a input voltage range higher than my requirement and a sufficiently high output current this seems to be a good fir for my requirement bur

I have attached the filled in excell for the same.

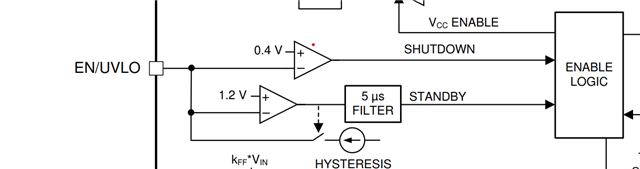

Also for the undervoltage enable logic to function (according to the block diagram given on page 16 of the datasheet) should the voltage on the UVLO pin be 0,4V or 1.2V. From my observation of the quickstart calculation when i give a UVLO of 25V the ratio of the resistors is such that the UVLo pin has 1.18V accorss it so can I assume that 1.2V on the pin measn that the ic enables a lockout ? The what id the 0.4V comparator for shut down mean ? I am assuming that the filter of 5us is a debounce and the voltage needs to be 1.2V at the pin for atleast 5us for the UVLO to work. But is there any way theat we can change the time of debounce ?

LM5146_quickstart_calculator_revB1.xlsm

Thanks,

G Karthik