Tool/software:

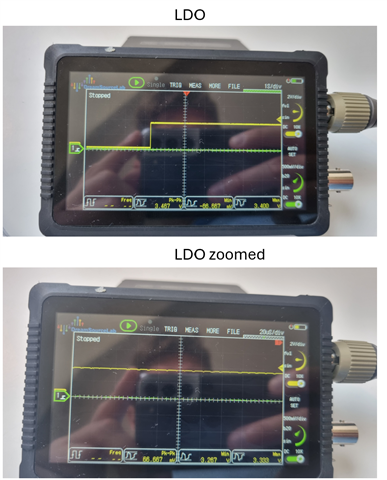

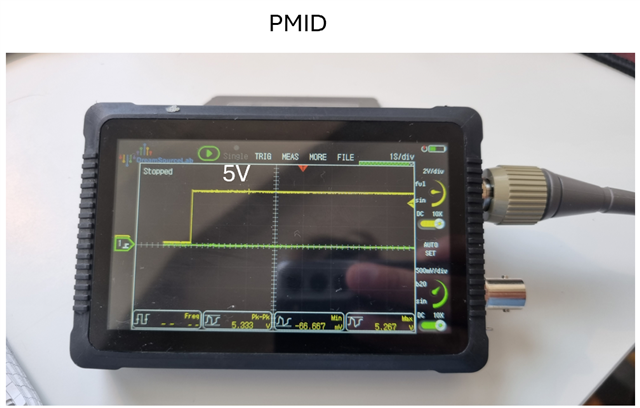

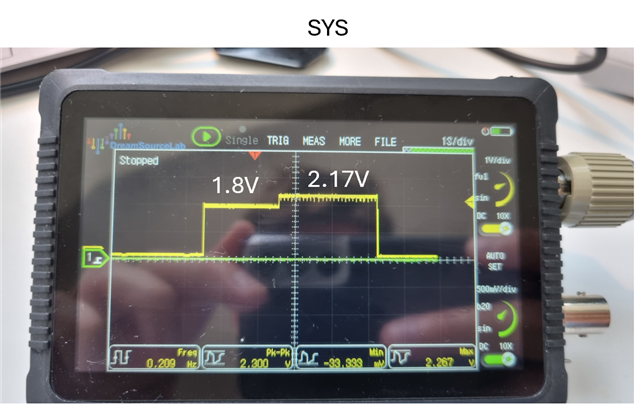

I am struggling to get the sys out to work properly, I want the default 1.8V and it seems to create this for a small period before the voltage suddenly increases to 2.5V (VIN not connected) or 3.6v (VIN connected). It does not seem to be any error messages and these are my register values. I put 0x01 to 0x04 because it generated an VIN_UV after disconnecting the input voltage:

Register 0x00 value: 0x41

Register 0x01 value: 0x04

Register 0x02 value: 0x08

Register 0x03 value: 0x14

Register 0x04 value: 0x0E

Register 0x05 value: 0x78

Register 0x06 value: 0xAA

Register 0x07 value: 0x7C