Other Parts Discussed in Thread: TUSB1044, TUSB564

Tool/software:

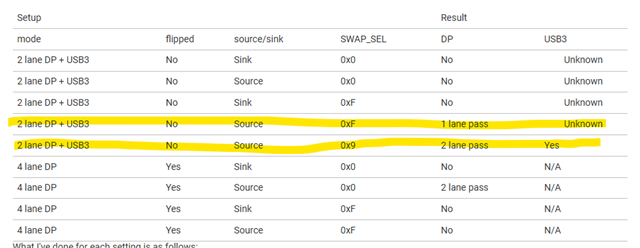

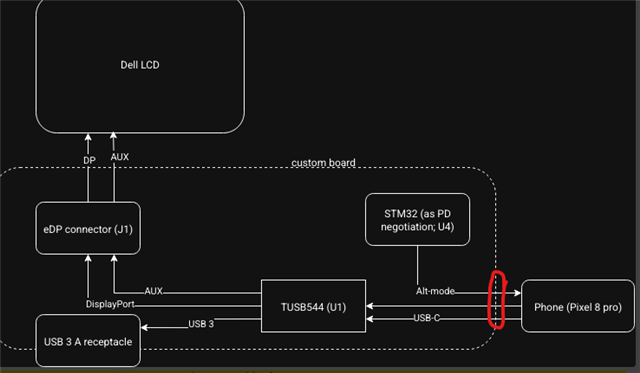

Hi, I have a custom USB-C hub/monitor that connects to a mobile device thru USB-C, and breaks out the DisplayPort signal to a eDP display and the USB3. 1 signal to a USB-A connector. I tried different signal configurations in TUSB544, but I get unexpected results:

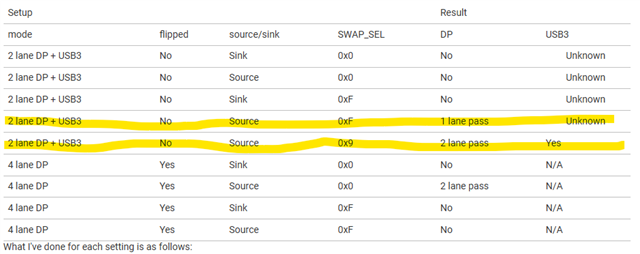

- 2 lane DP + USB3 in sink mode: USB3 works fine, however DisplayPort can't finish link training (no clock recovery at all; no matter what gain/VOD config I use)

- 2 lane DP + USB3 in source mode (remember this is a sink device): DP link training fails; most of the time lane 0 can't finish clock recovery, but when it can, it can't finish symbol locking; lane1 always finishes clock recovery and symbol locking. This also doesn't change when I change gain/VOD configs (I didn't test USB3 in this mode)

- 4 lane DP, flipped, in source mode, and flip AUX lines (so it's in normal orientation): link training finishes, using minimum gain/VOD setting

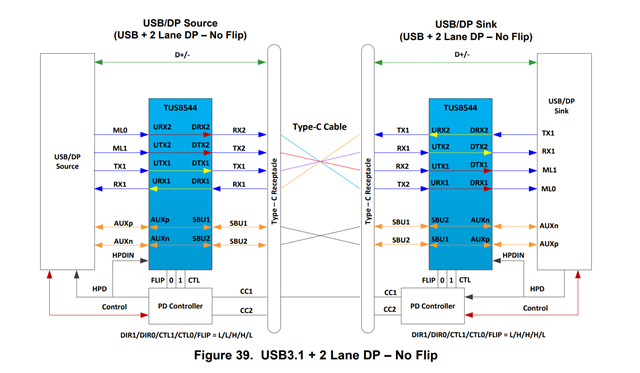

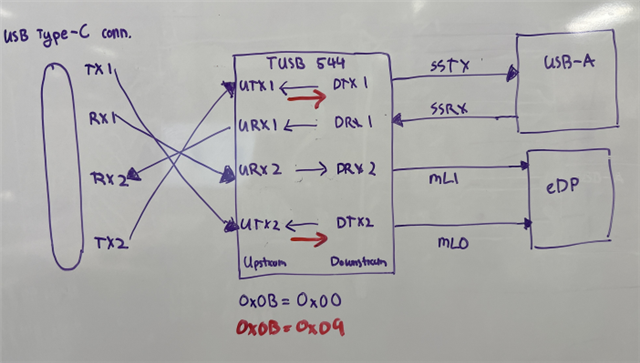

I don't have my schematics at the moment, but from the PCB the lanes are connected as follows:

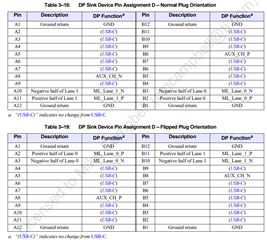

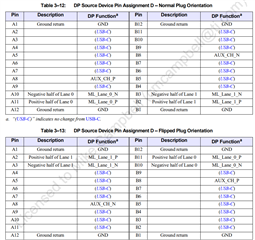

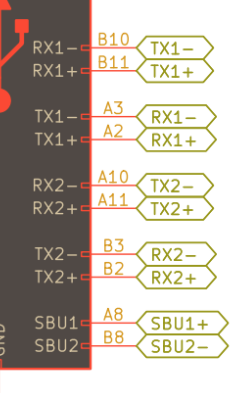

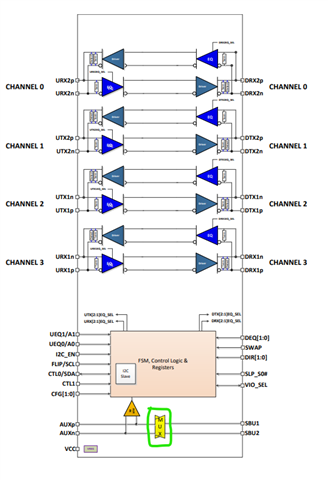

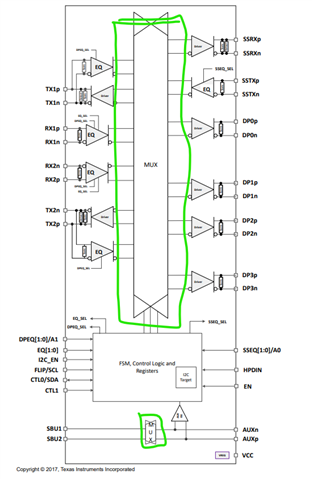

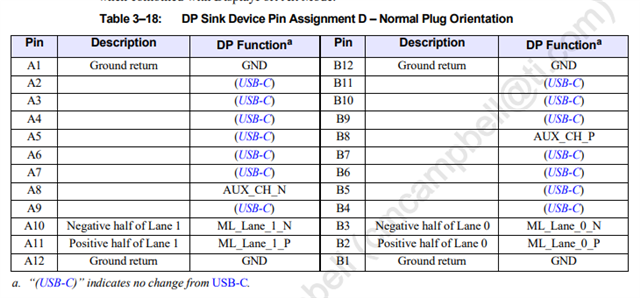

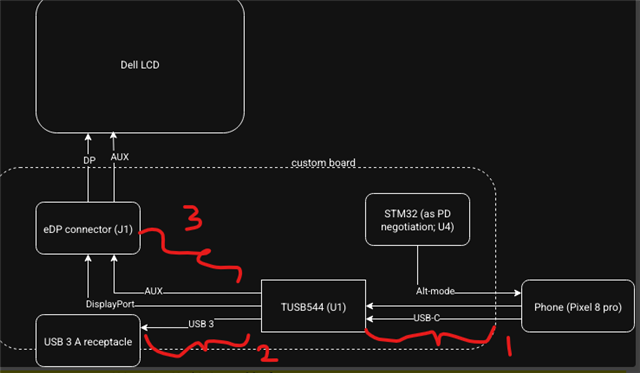

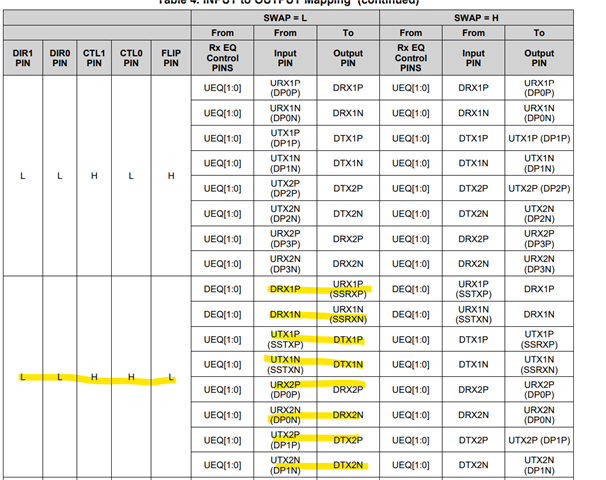

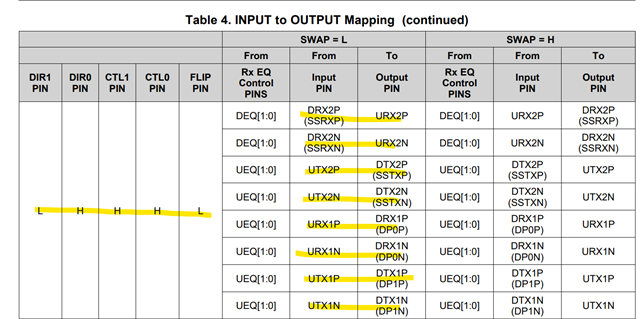

- USB-C RX2+/- (B2/B3) => UTX1+/-, DTX1+/- => DP1+/-

- USB-C TX2+/- (A10/A11) => URX1+/-, DRX1+/- => DP0+/-

- USB-C RX1+/- (A2/A3) => UTX2+/-, DTX2+/- => USB3-A SSTX+/-

- USB-C TX1+/- (B10/B11) => URX2+/-, DRX2+/- => USB3-A SSRX+/-

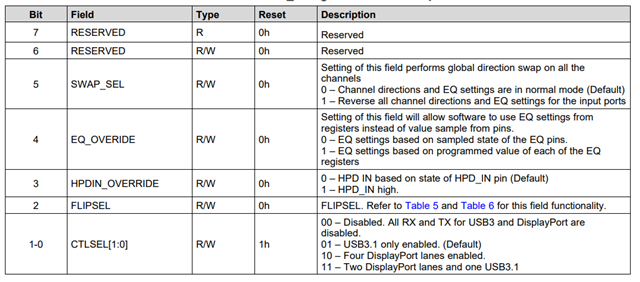

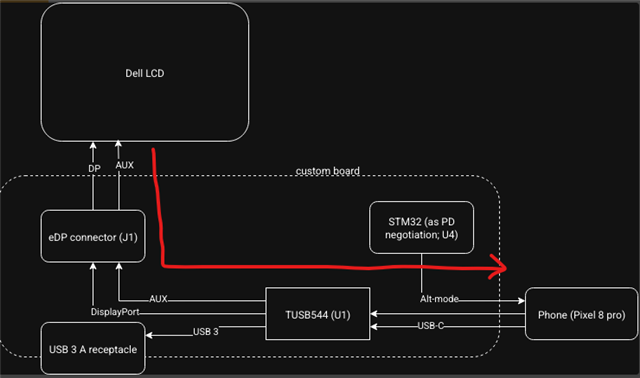

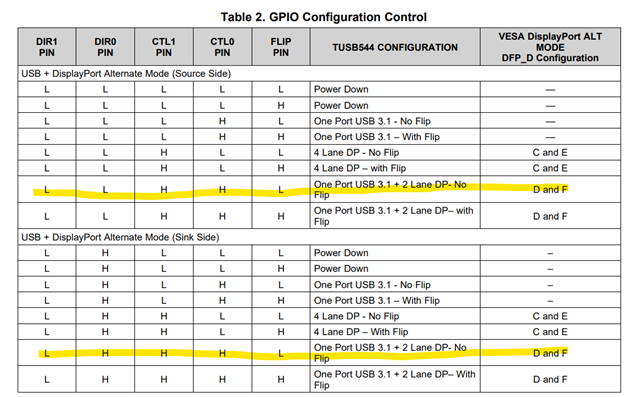

Given this connection, the expected setting should be: CTL[1:0] = 0b11, DIR[1:0] = 0b01, FLIP = 0, SWAP = 0

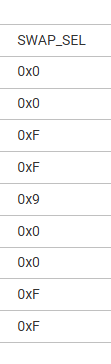

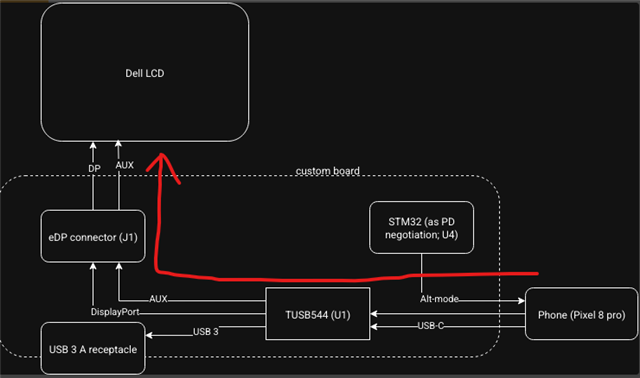

However, the only setting that worked for me is: CTL[1:0] = 0b10, DIR[1:0] = 0b00, FLIP = 1, SWAP = 0, and set AUX_SBU_OVR = 0b01

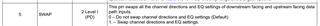

Please let me know what I'm doing wrong. I also would like to know what the sink/source modes in TUSB544 actually change, and how it relates to SWAP, since the datasheet doesn't seem to explain either. The only difference I can observe regarding sink/source modes is in Table 4 of the datasheet, is whether e.g. DP0P/N markings appear on the input or output side. Thanks in advance!