Other Parts Discussed in Thread: LM3409

Tool/software:

Hi,

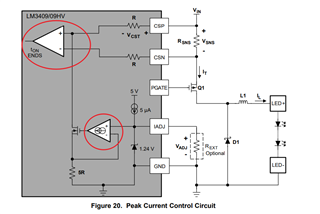

My customers are curious about the detail logics of peak current control and the tolerance of Vcst when adding an external voltage on Iadj pin:

1. Can you explain in details that how the two comparators is triggered and the each output status when the Vsns is hitting Vcst and peak current threshold ?

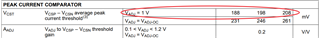

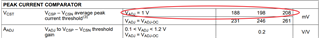

2. What is the tolerance of the Vcst when adding an external Vadj on Iadj pin (the datasheet only listed the min and max value with 1V Vadj, how to calculate when the min and max value with like 0.6V Vadj? Is it linear like the typical value) ?

3. What internal parameters might have affects on the tolerance of the Vcst when adding an external Vadj (Customers have concerns that the max value of Vcst might lead to too big current)?

BR,

Manu