Tool/software:

Hi~

I have a few questions.

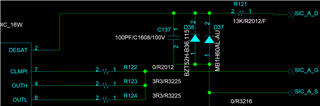

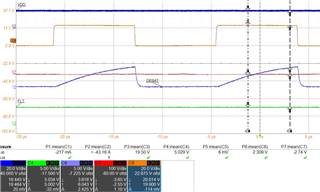

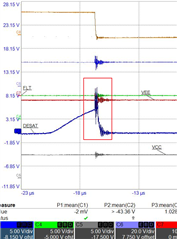

1. When I designed and measured the Desat circuit as shown below, it worked as shown in the measured waveform. Please check if it is working normally.

2. If the desat setting value is 7.52V, how does desat work? If it gets bigger than the fixed value of 9V, does desat work, and if it gets smaller, does desat not work?

3. When the Gate turns On and Off, a peak noise occurs in the Deset waveform. Why does this occur?

4. What is the range of CBLK values for the desat circuit?