Tool/software:

Hi;

(Apologies that this question has to do more with manufacturing rather than technical specs - I'm in the learning phase with this IC).

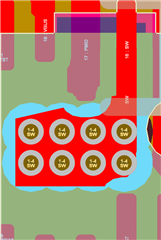

I am trying to develop a design using the BQ25628E. In the datasheet for this part, the PCB Layout guidelines specify using "many vias" in the path from the SW pin through CBTST and out to the inductor. The guidelines illustrate what seem to be very small vias here (0.1mm? 0.15mm?), which seem to be on the 'difficult' end of the manufacturing spectrum (at least, when referring to capabilities listed by JLCPCB and similar manufacturers' websites).

I'm curious if larger vias may be used here, or if any elaboration might be made on the manufacturability of these vias? I get a lot of DFM errors about annulus spacing when trying to fab a board using this part, and I'm curious if there's particular language I should use in conversation with a manufacturer about these, or any general tips for success having a board made with these tiny fellas.

Thank you!