Tool/software:

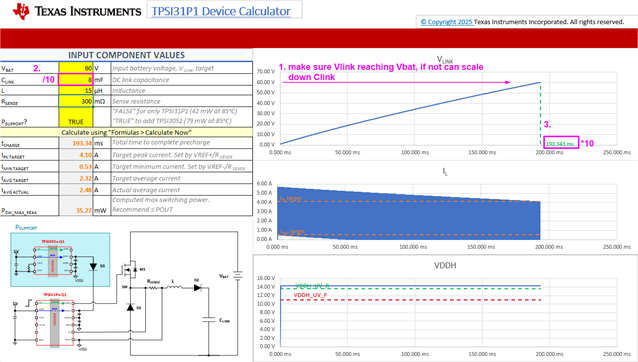

Hi, a few questions from the implementation point (this is for a lower voltage, 60V max system with about 40-80mF of capacitance)

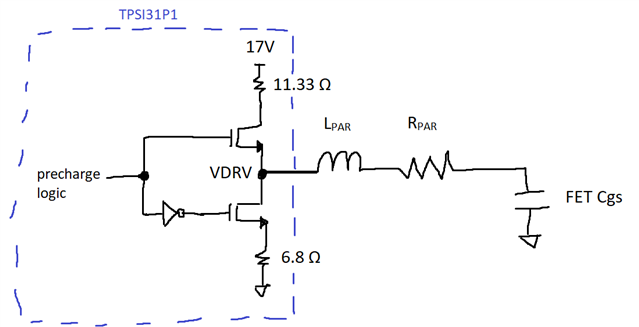

- What is the function of a safety cap/resistor network across the output that's present in the EVM design? Is that normally present in a production design?

- Any specific requirements for the diode D1 besides voltage/current? Does it have to be an Ultra fast recovery type?

- Same question for selecting the main FET- any specifics?

- The datasheet mentions a FET M2 to prevent reverse current flow, while the dev board goes with a diode- what is the rational there?

Thank you!