Other Parts Discussed in Thread: LM5160, LM5160DNTFBKEVM

Tool/software:

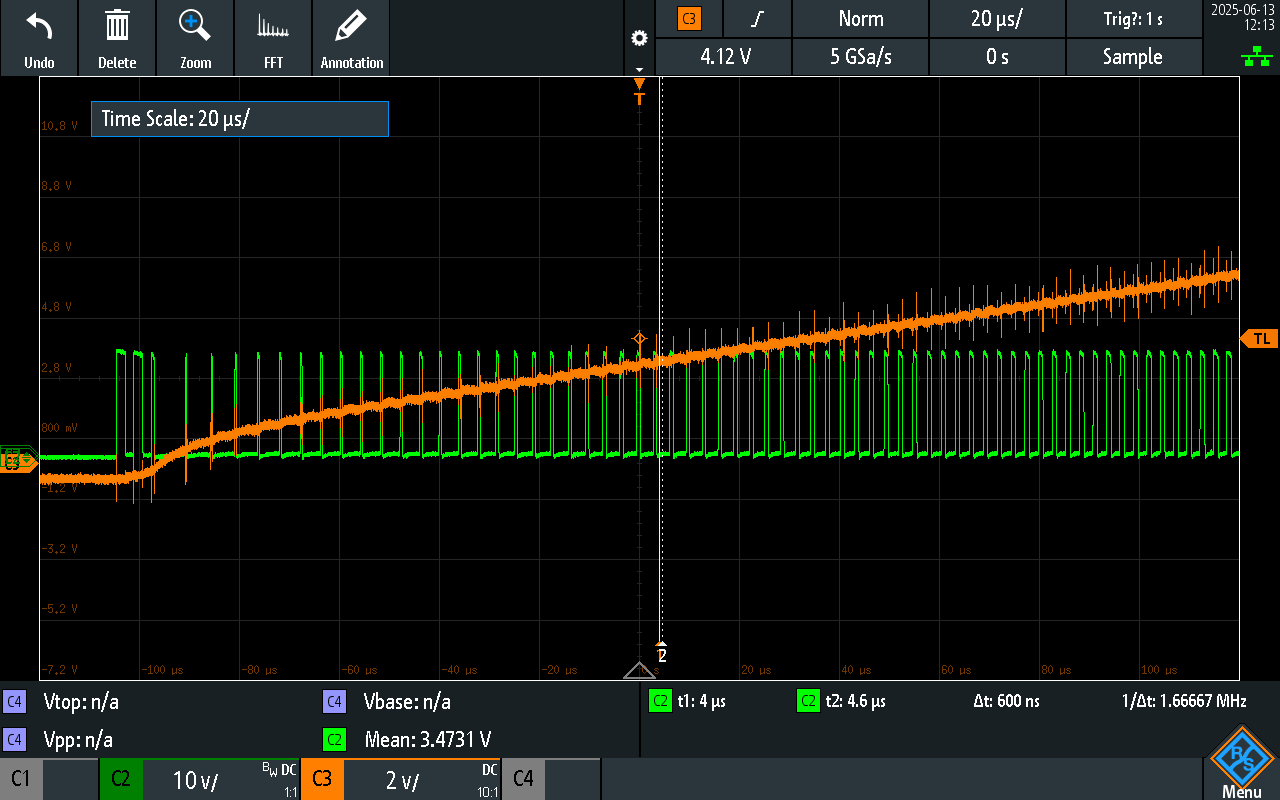

we test the LM5160 EVM board. we can find the PWM signal of chip is stop during power supply start-up; stop time is about 40us;

the peak current value of transformer primary side is about 430mA;

why dose the chip output stop?

- Yellow is PWM(sw pin);

- Blue is output voltage;

- Green is FB pin;

- Red is transformer primary side current;

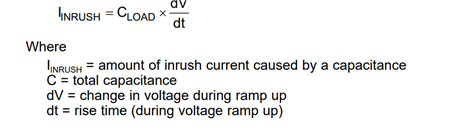

where C_LOAD=output capacitance, dv~ Vout, dt=Tss.

where C_LOAD=output capacitance, dv~ Vout, dt=Tss.