Tool/software:

Hi,

We are using UCC24612-2 in LLC sync FET drive. (2 FETs, center tapped architecture). Integrated Leakage inductance in LLC transformer for Lr.

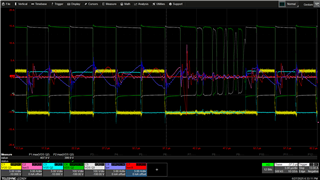

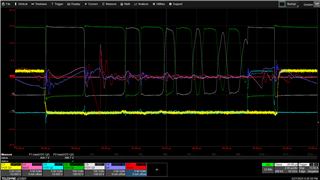

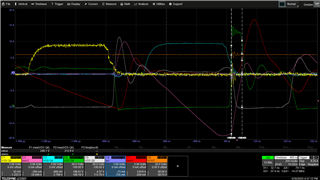

We are seeing frequent false turn ON 1 of the sync FET gate pulse during burst mode of LLC - Under No load.

We are seeing infrequent false turn ON of both FETs back to back gate pulse during burst mode of LLC - Under No load.

Q4, Q5 are the sync FETs. Q2, Q3 are Half bridge LLC Primary FETs. Isec5, Isec8 when positive are flowing from source to drain.

This is causing our Sync FETs to go to avalanche, please suggest how we can avoid this. Since we have substantial leakage in our LLC transformer, the kickback too high during Sync FET off. I understand that UCC24612 increases the blanking OFF time if it detects a false turn ON by checking if ON time == Minimum ON time but that at the start of DCM, the first false cycle of each sync FET is enough to take FET to avalanche.