Other Parts Discussed in Thread: LM5164-Q1,

Tool/software:

Hi expert,

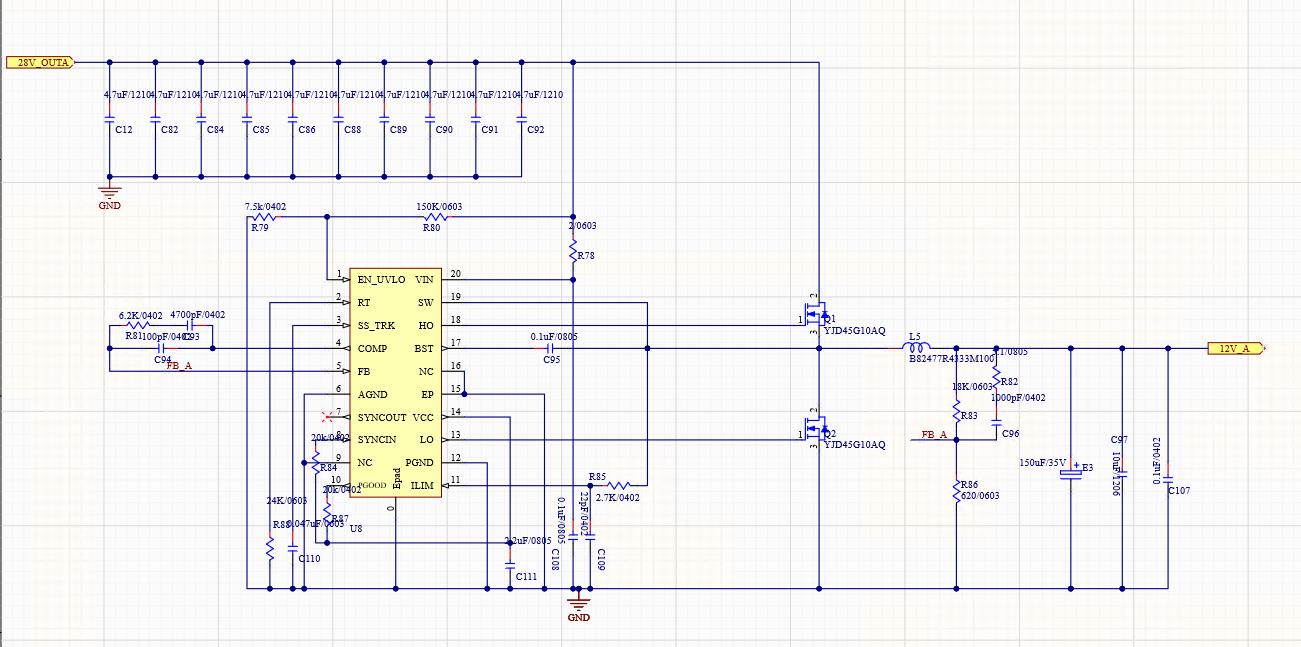

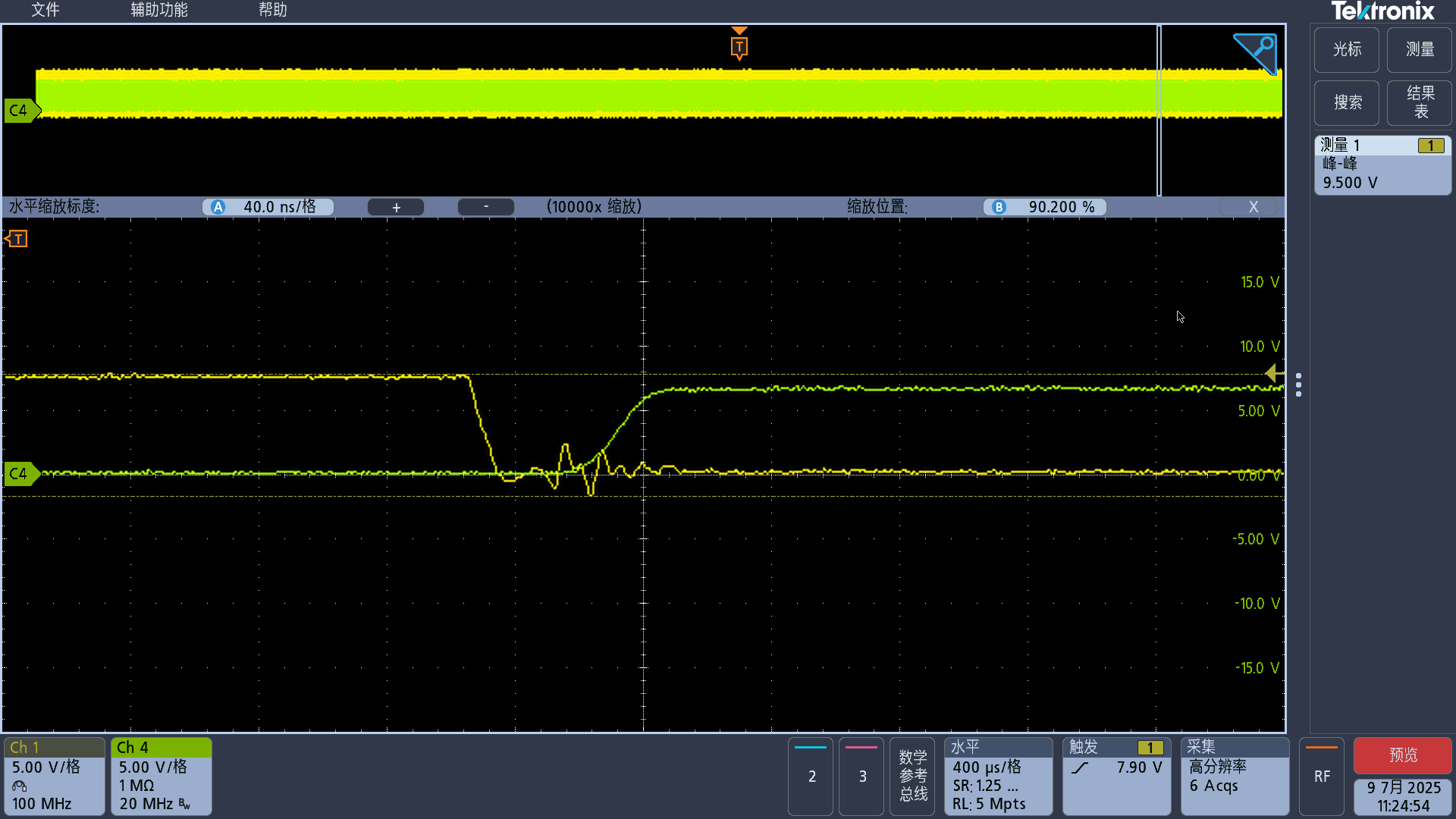

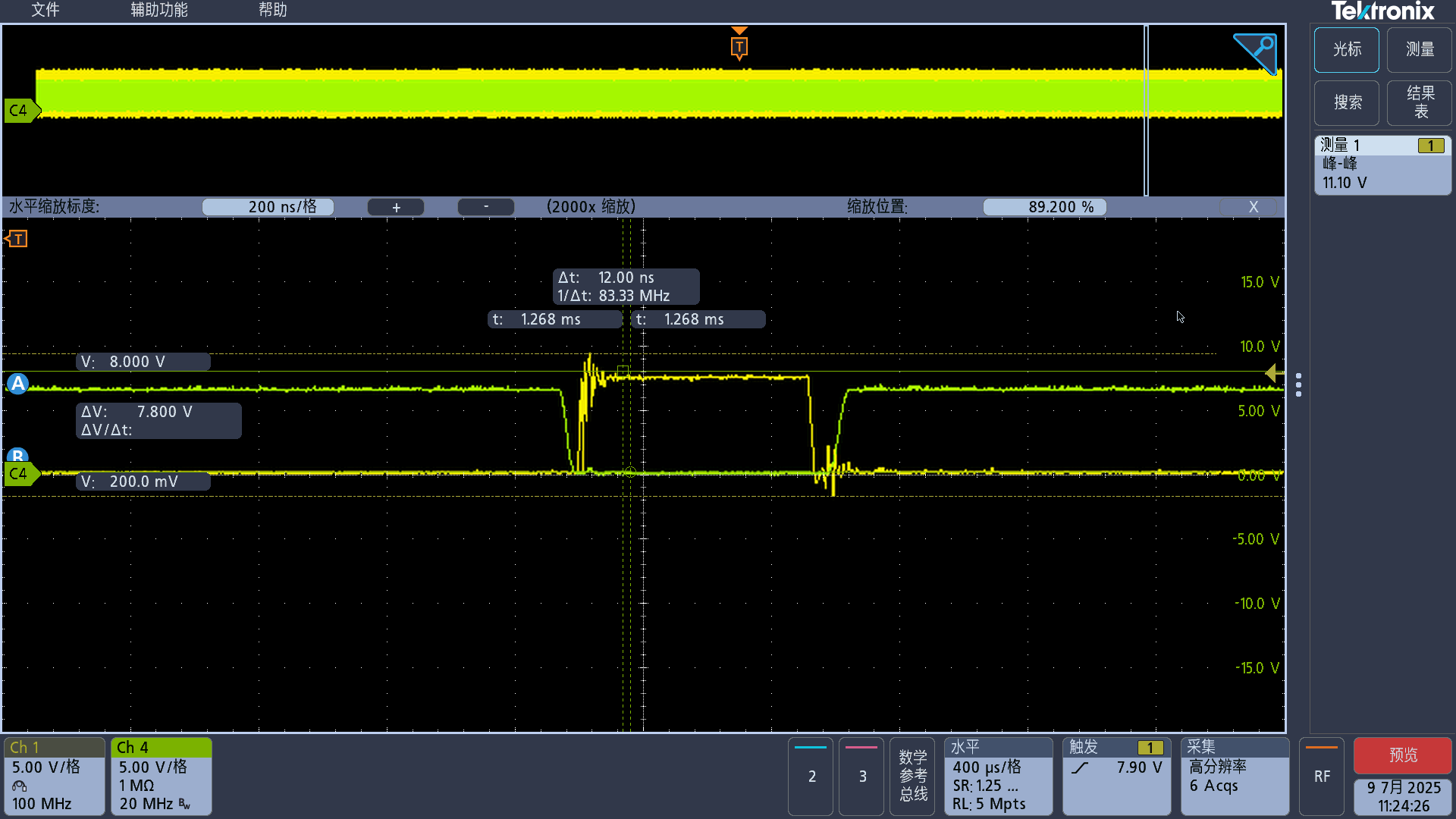

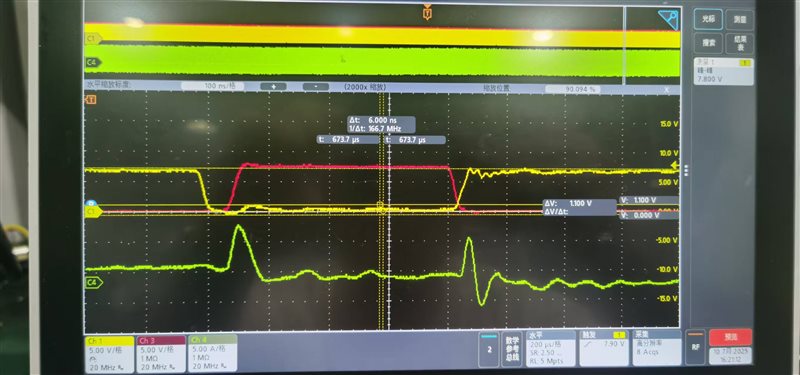

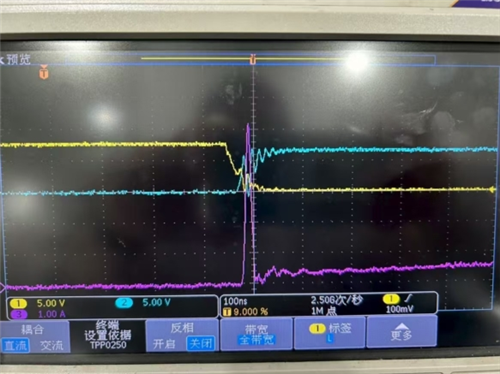

My customer (Enpower) is testing LM5164-Q1 and found THE two MOSFETs of BUCK circuit would be shoot-through by Vgs ringing. Do we have some suggestions to avoid the shoot-through? Thanks.

Best Regards,

Ryker