Tool/software:

Hi,

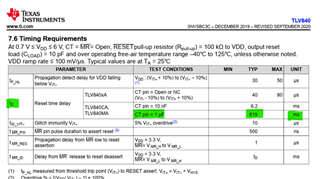

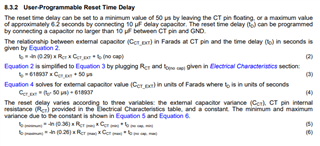

My customer is using the TLV840. The timing in question is tD on the datasheet and is the delay from MR to Reset release. If we are using a 1uF, 10% capacitor connected to pin 5 (CT) and the datasheet indicates this has a tD of 619 mS typical, or 680mS with 1.1uF.

However, we're seeing about 700mS delay instead of 619ms. Are there min and max conditions for the tD that I should expect? The reason for asking is that the in-circuit test needs to have bounds on the timing.