Tool/software:

Hi there to all,

I wanted to obtain a 30V/1.5A CC/CV regulator and designed two variant with LM25117, according to the datasheet page 34 and application note SNVA829 but I have some problems with them. Hence I wish solve them together.

NOTE: There is no overheating generally but the inductor is quite warm at ~ 45C. SHDN and IMON ports are not connected anywhere in the schematics.

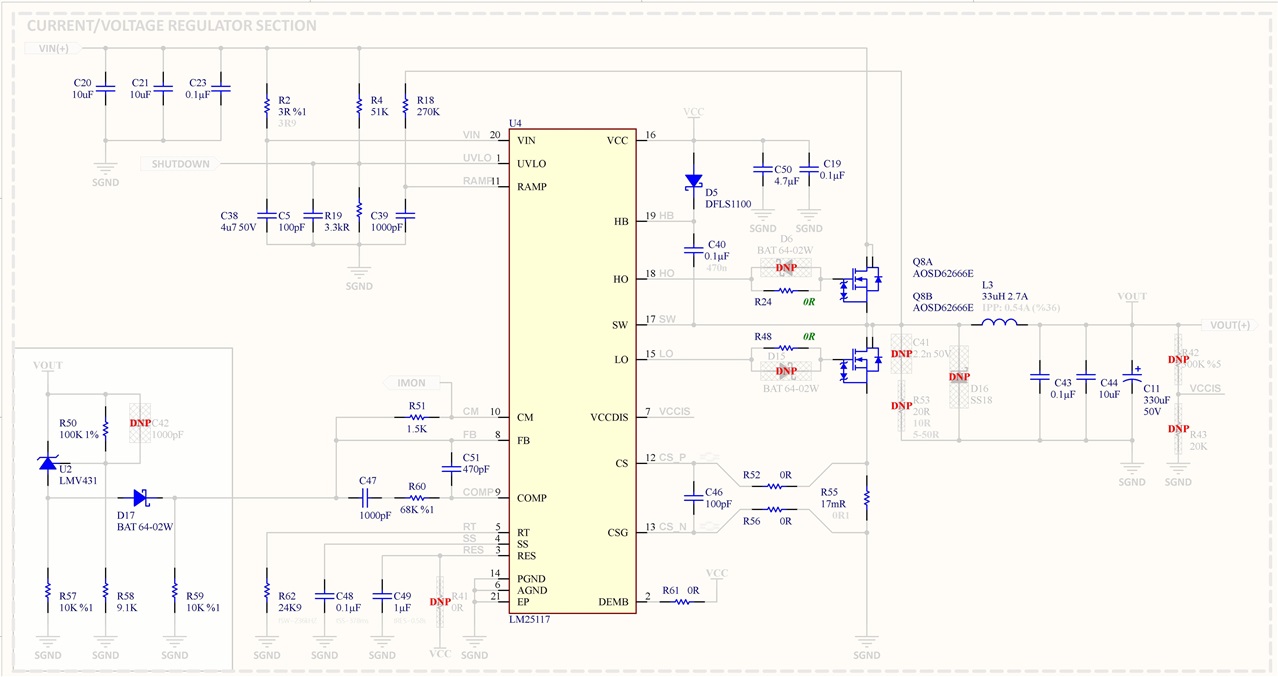

For the variant-A that follows the datasheet,

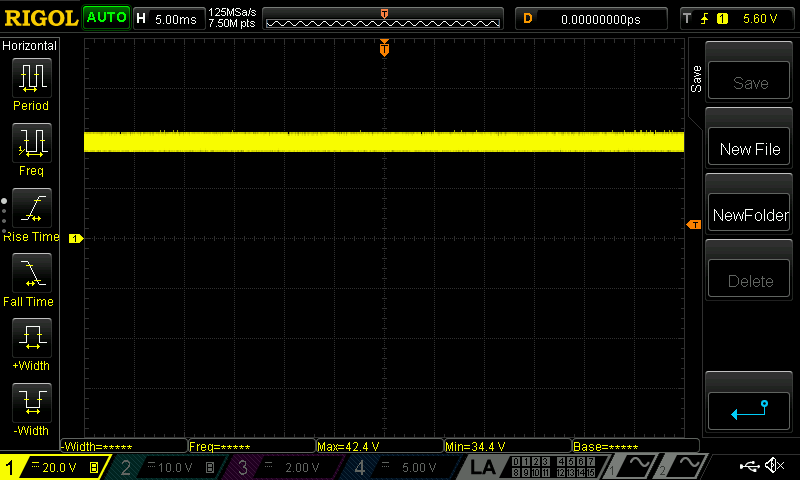

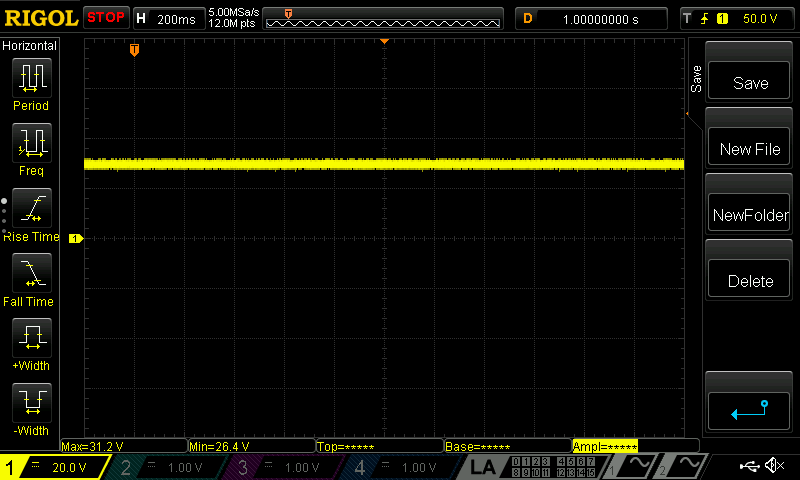

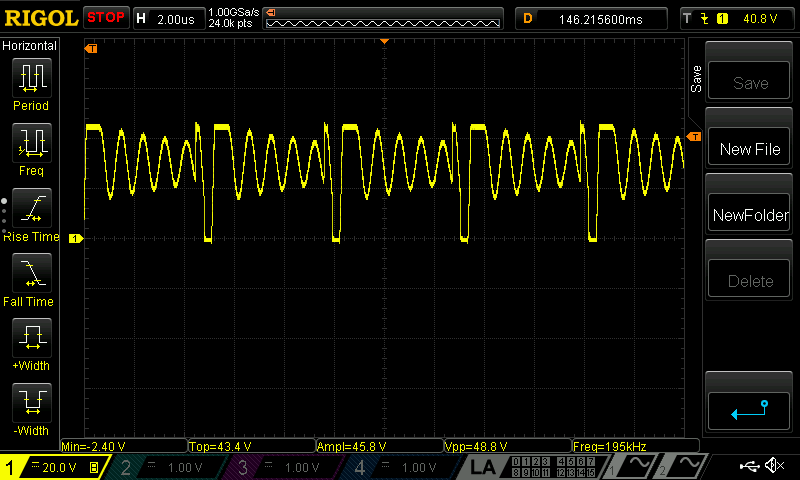

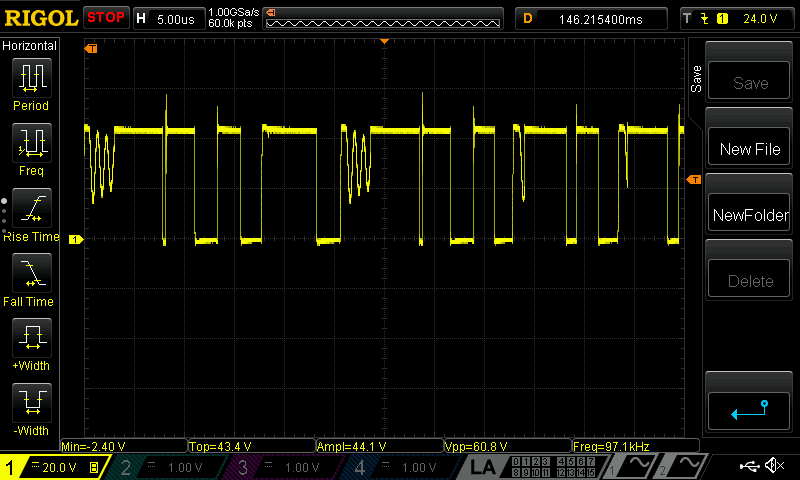

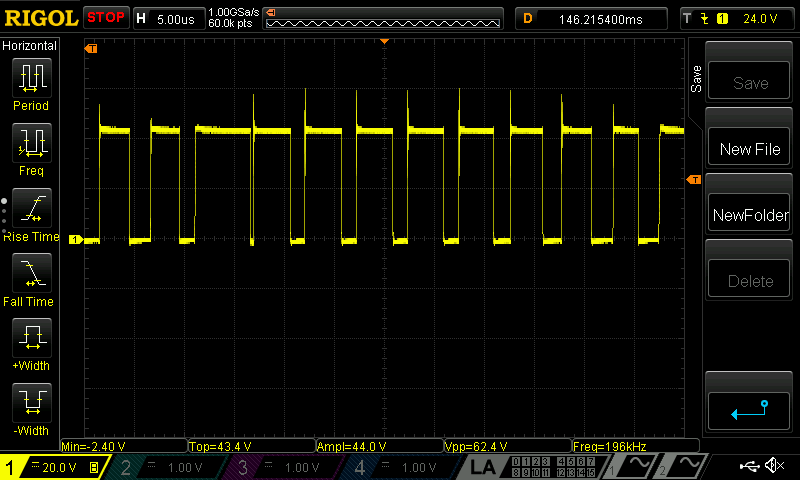

- For now, output voltage is same as the input that is 36V and output current limit is only limited by the source so there is no CC and CV control. I am still testing and the schematic is shown below.

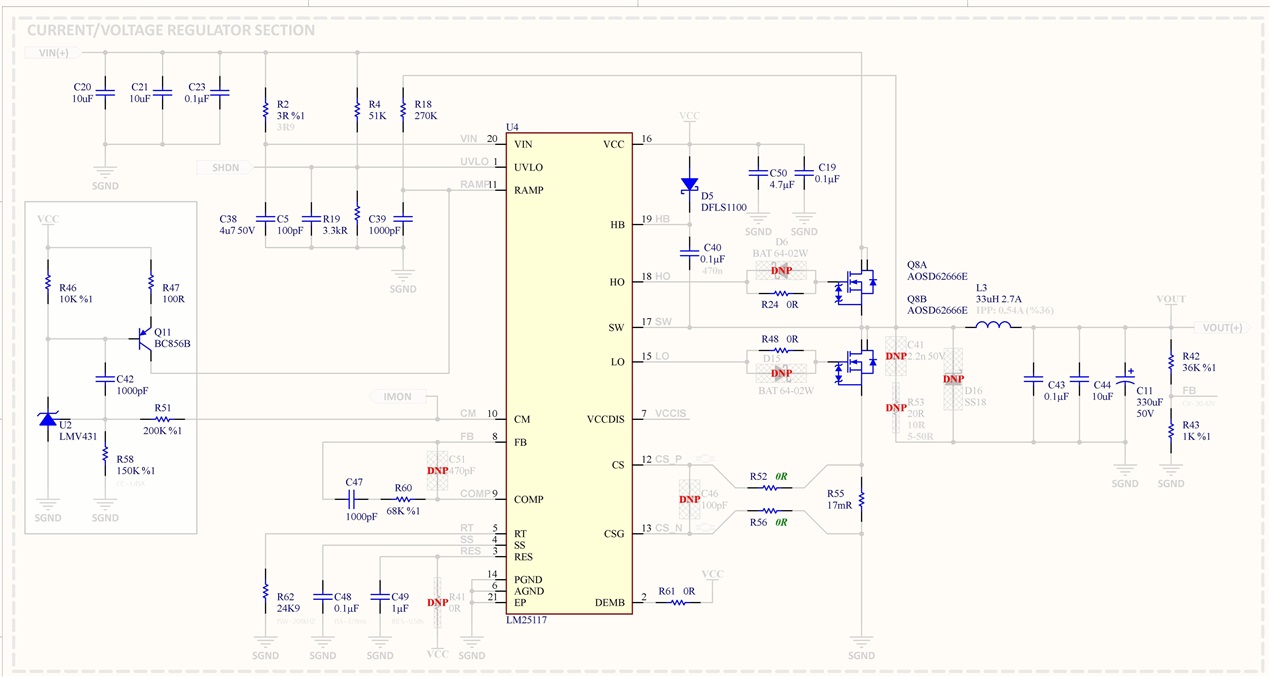

For the variant-B that follows the application note,

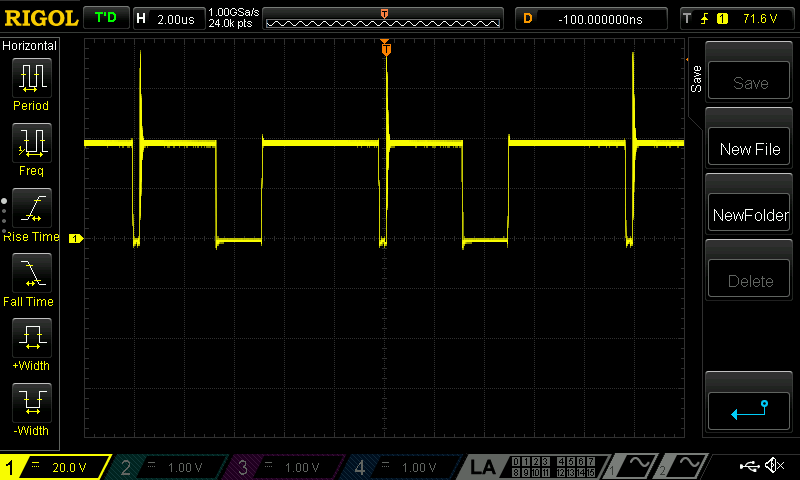

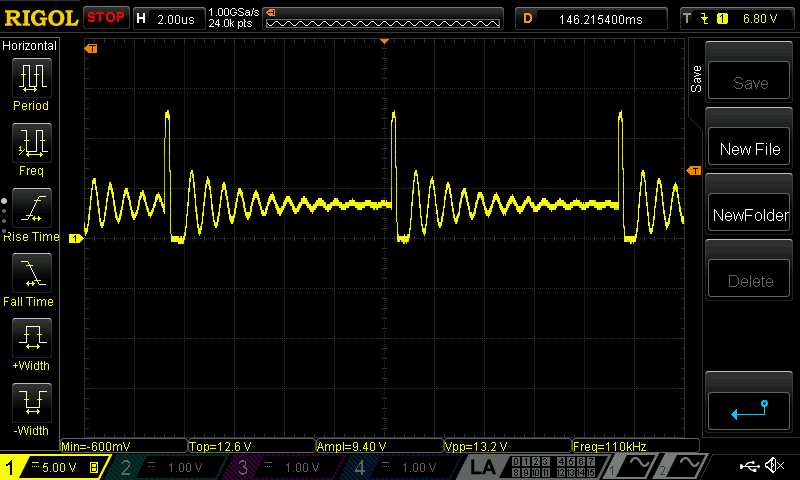

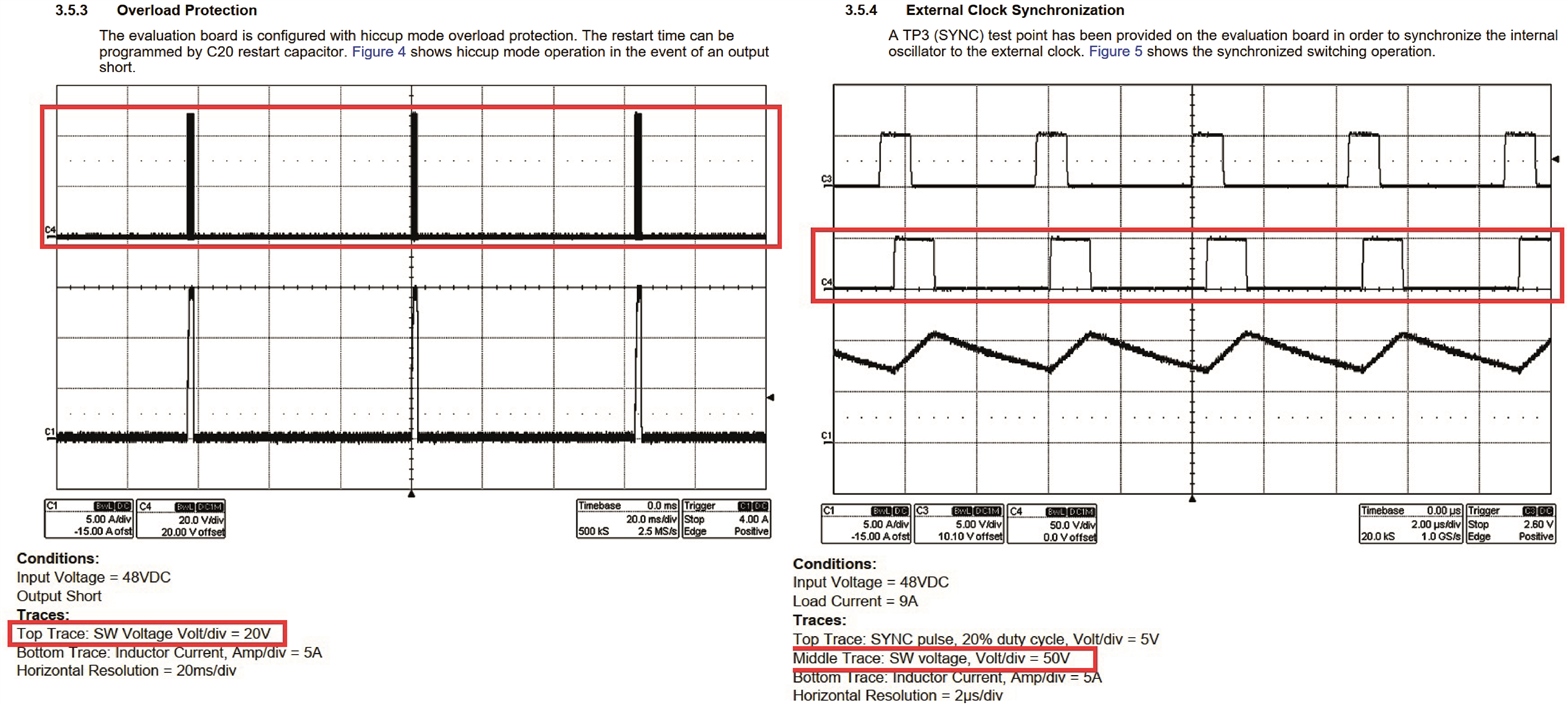

- For now, I can control the output voltage that is ~30V but when the load current is reaches ~430mA the IC enters the hiccup mode. Somehow it cannot supply more than this level of current and I cannot read any CM output for load current in terms of voltage. For testing, I removed the R51 and Q11 to disable the CC control. The schematic is shown below.

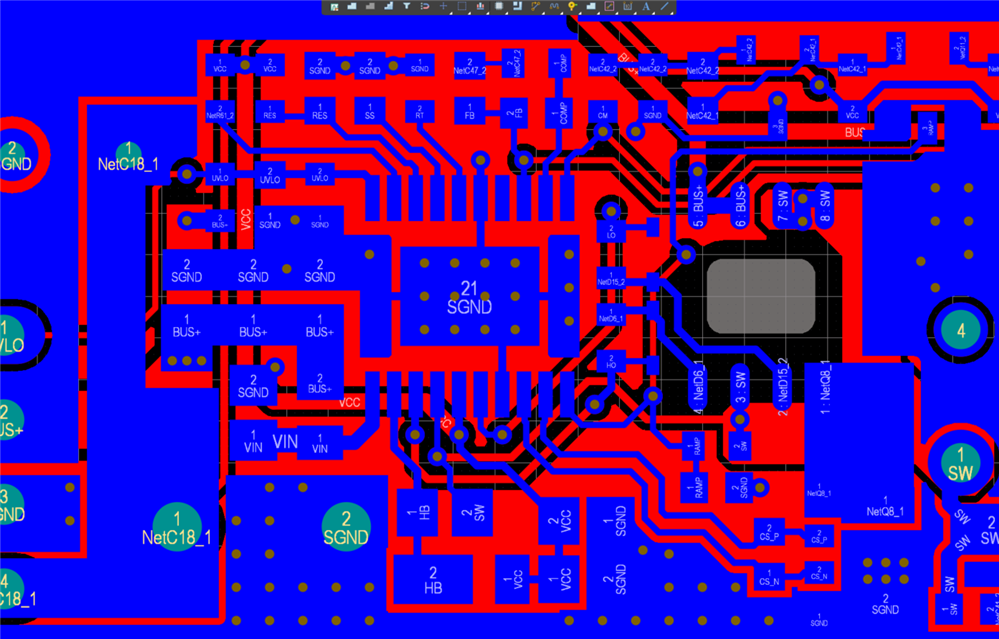

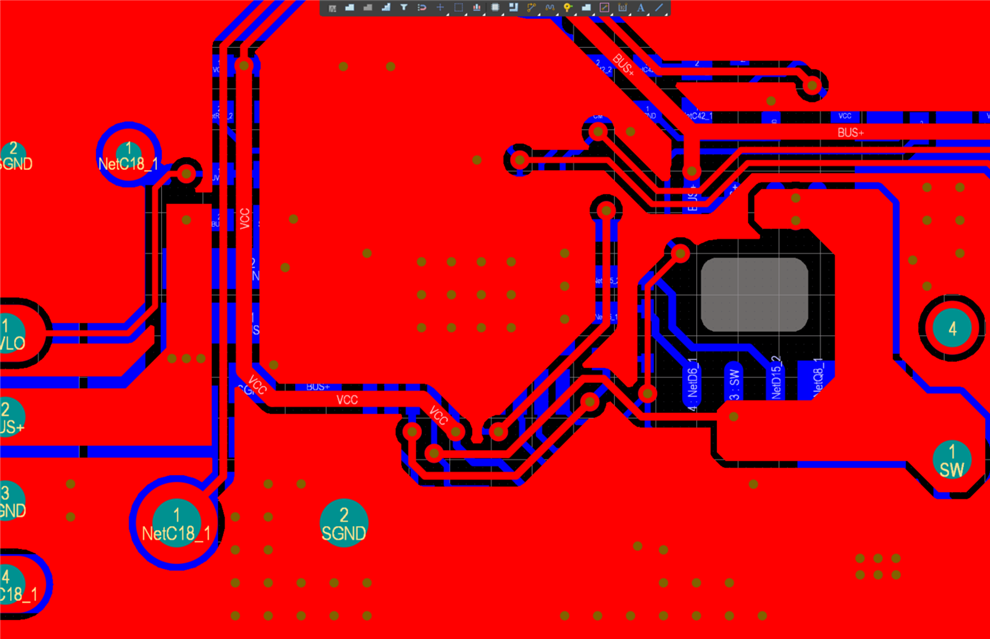

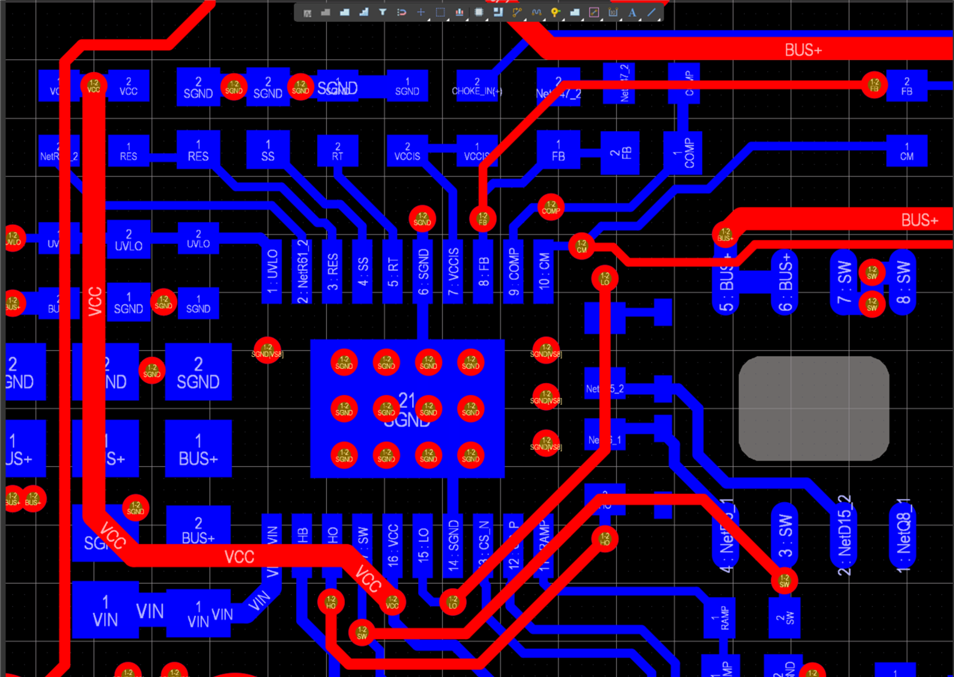

The layouts are quite same and shown below,

I am still testing and waiting for your comments, opinion and experiences.

Thanks for all and have a nice day!