Other Parts Discussed in Thread: TPS2HCS08-Q1

Tool/software:

We're using the TPS274C65AS in a system with a host microcontroller, DSPI=0, CRC_EN=0. In some circumstances, the microcontroller might need to restart or will otherwise lose its in-RAM state, which will also cause the in-memory copy of what SW_STATE ought to be to get lost. Saving this shadow copy to persistent storage on each change would cause significant wear, so we'd like to avoid that.

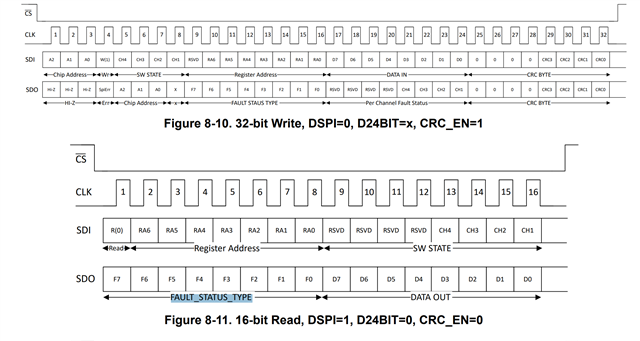

We now want to be able to read back the current state of SW_STATE from the TPS274C65 without accidentally changing the state of any output (and thereby possibly powering down/starting a device downstream). However, as far as I can tell, this is not possible because every read will implicitly set the current switch state from the lower nibble in the first byte of the transaction. E.g. reading SW_STATE will return the current state of SW_STATE, but since we had to supply some new value as part of the SPI transaction header, the outputs will toggle accordingly after the transaction ends.

Is there any way we can query the value of SW_STATE without disturbing it? I haven't tried it but I could imagine playing some trick like doing multiple operations without releasing CS or something like that, depending on if that is even possible and how SW_STATE is latched, but none of that is really specified in the data sheet. I'd appreciate any input.

Thanks!