Other Parts Discussed in Thread: UCC5870QEVM-045,

Tool/software:

Hi,

We are currently evaluating the UCC5870QEVM-045 and have questions about the Function BIST feature.

1.After setting the GATE_OFF_CHK bit to 1, I write 1 to CLR_STAT_REG to clear the fault, but the fault is not cleared. If I write 1 to CLR_STAT_REG twice, the fault clears. Why does this happen?

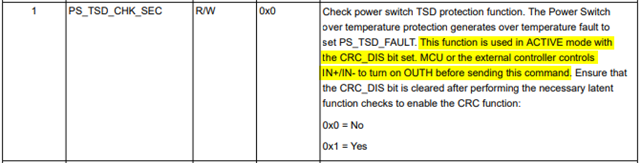

2.Writing 1 to PS_TSD_CHK_SEC does not generate a fault. Does this BIST have constraints—such as requiring a thermistor connection—before it can be used?

Thanks,