Other Parts Discussed in Thread: DRV8353RH-EVM, LM5008

Tool/software:

Hi TI,

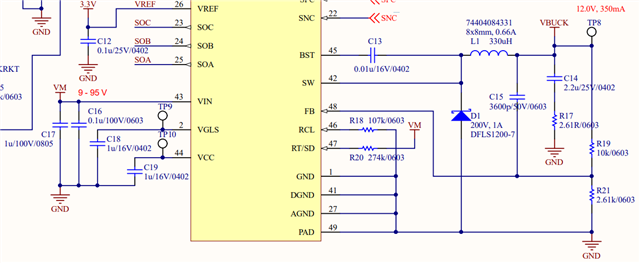

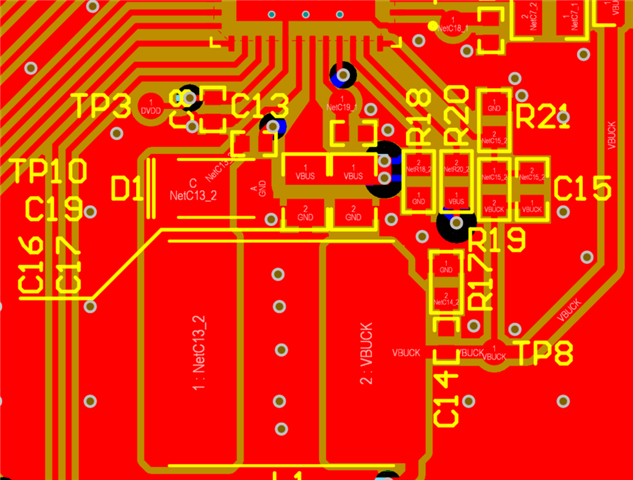

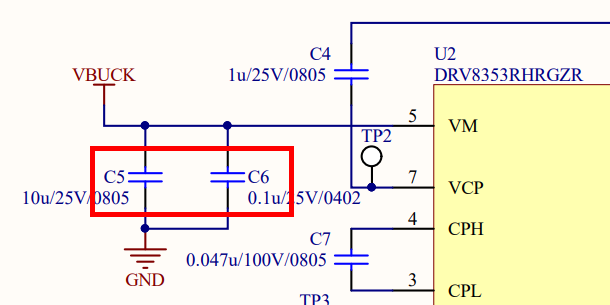

I follow the components to design LM5008A in DRV8352RH-EVM.

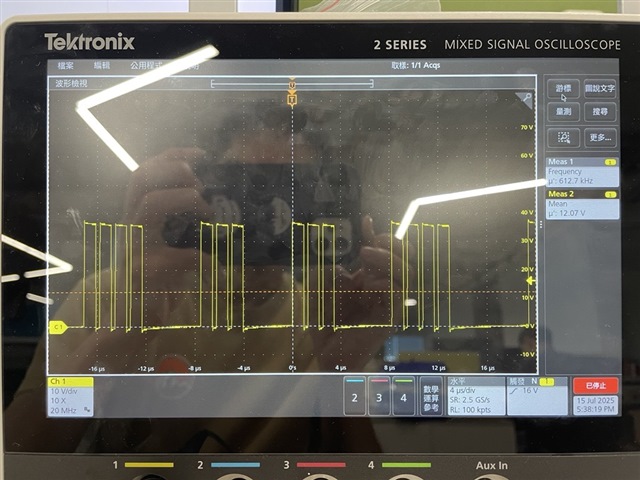

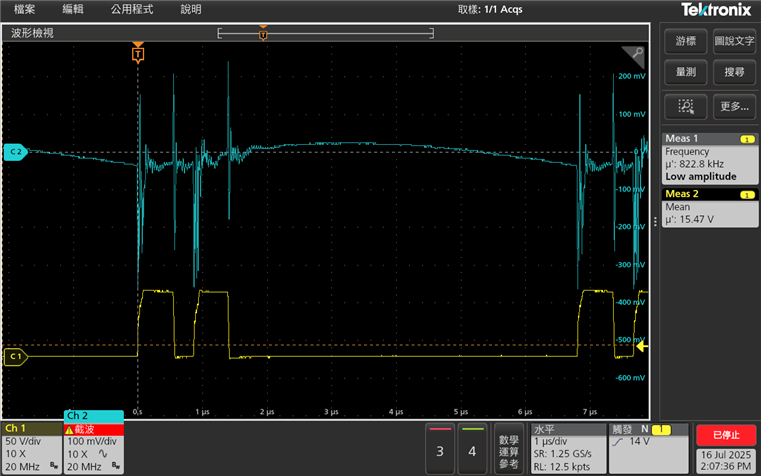

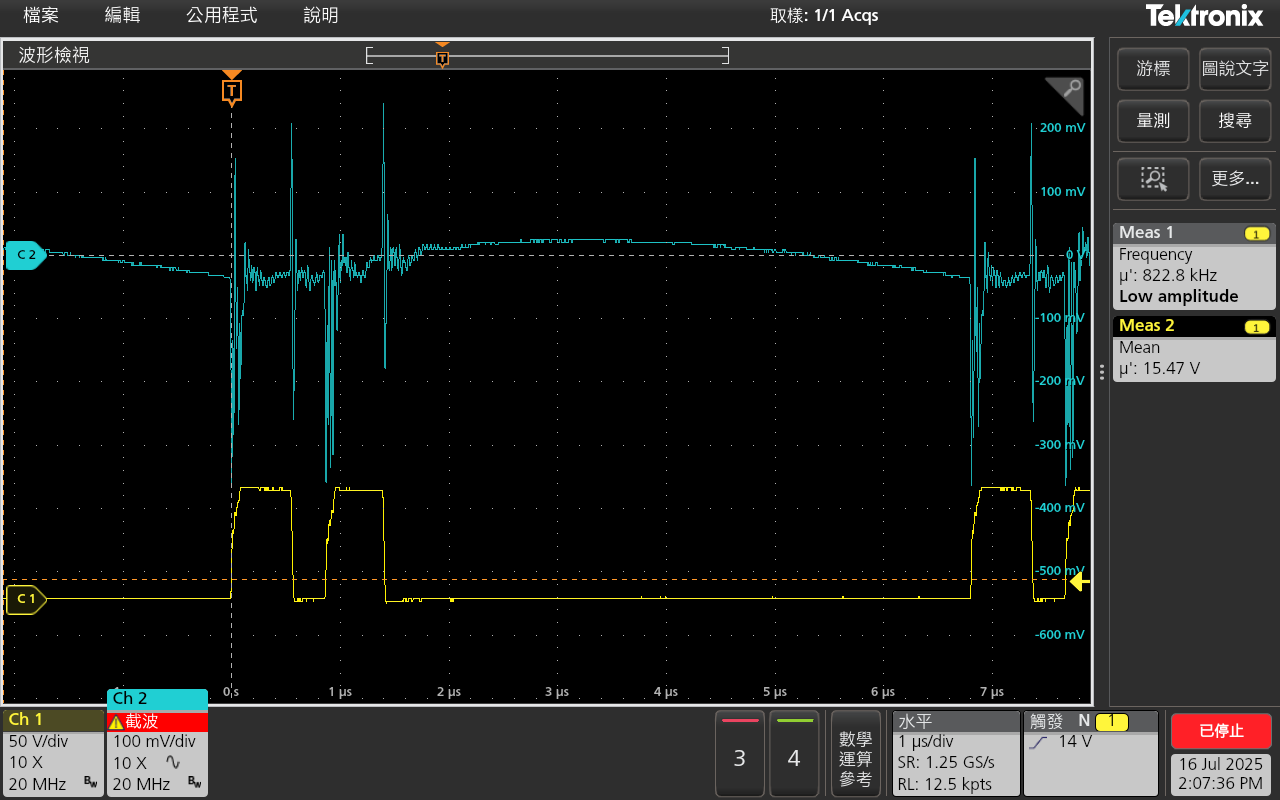

When input is 36~48V and output is 12V / 350mA, the Vsw is unstable and jittering as below.

Please help to solve this situation.