Other Parts Discussed in Thread: UCC27212

Tool/software:

Hello,

I am experiencing Glitches with my DCDC Converter which cause the Highside MOSFET to turn off earlier than the HI Signal.

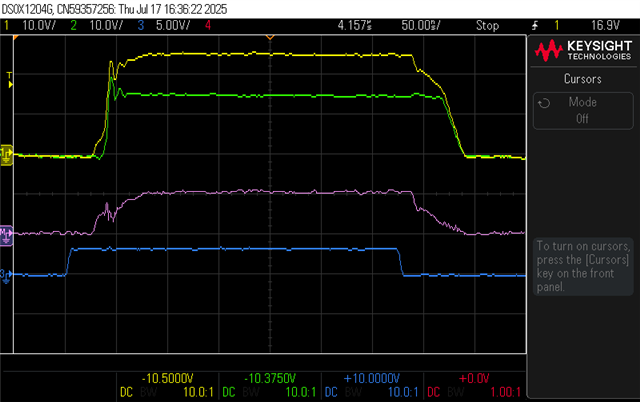

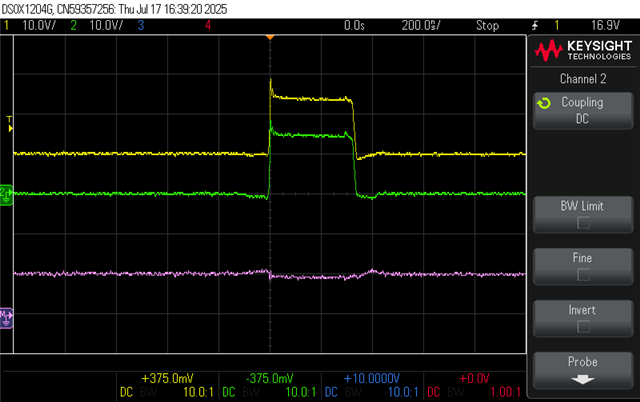

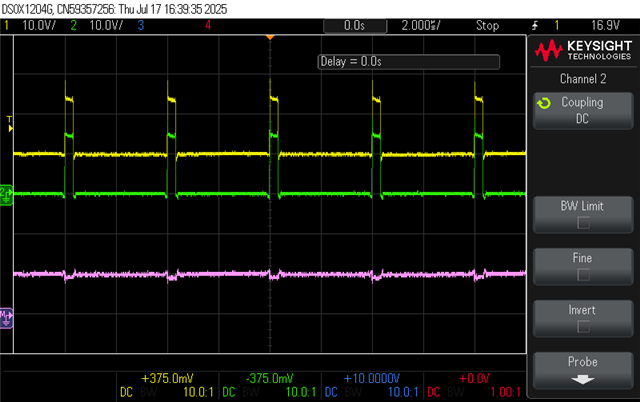

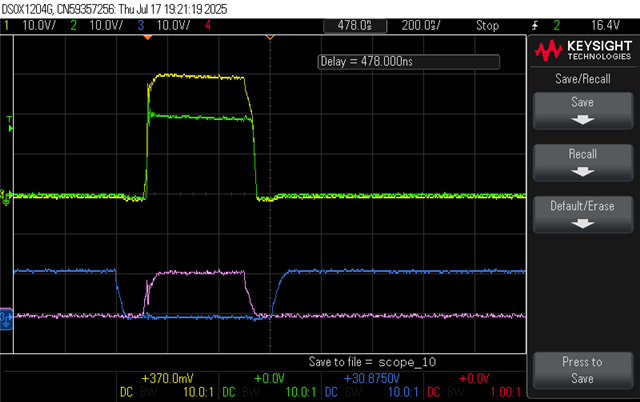

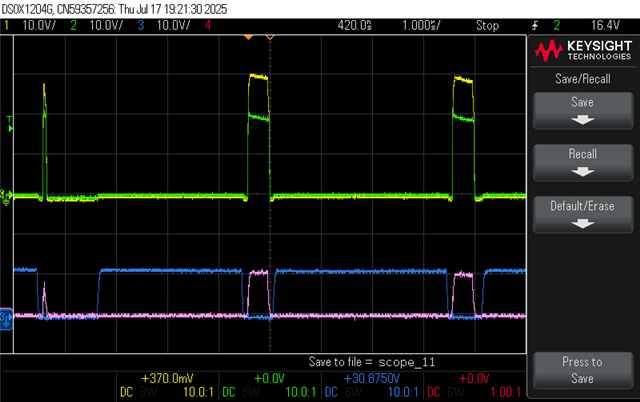

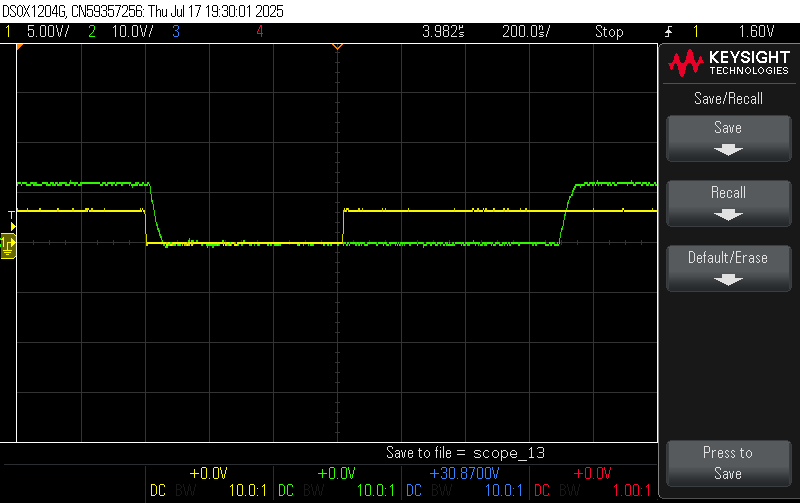

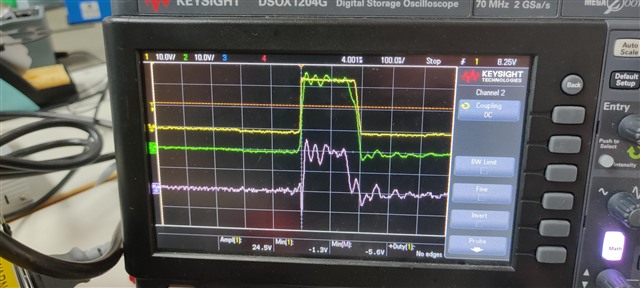

Normal Pulse (200ns)

- CH1 = HS - GND

- CH2 = HO - GND

- Purple = HO-HS

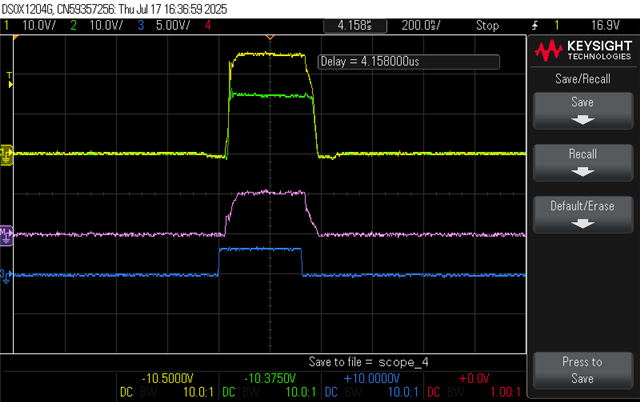

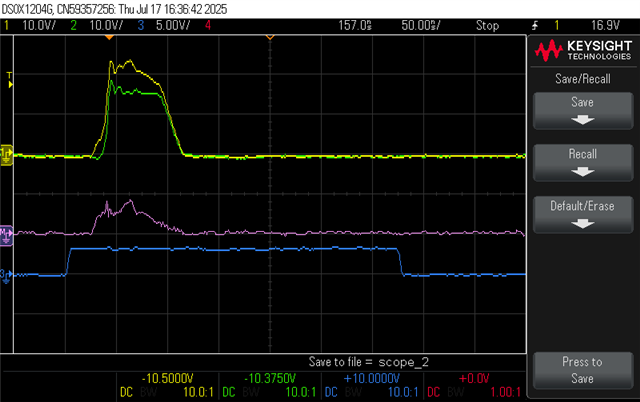

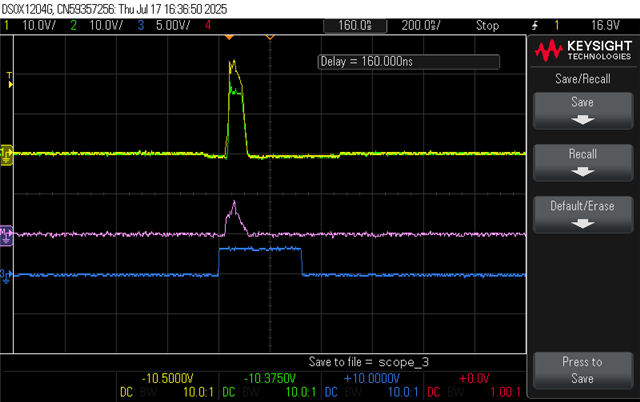

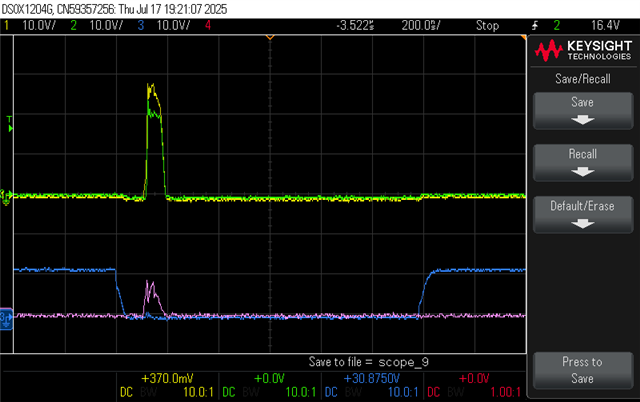

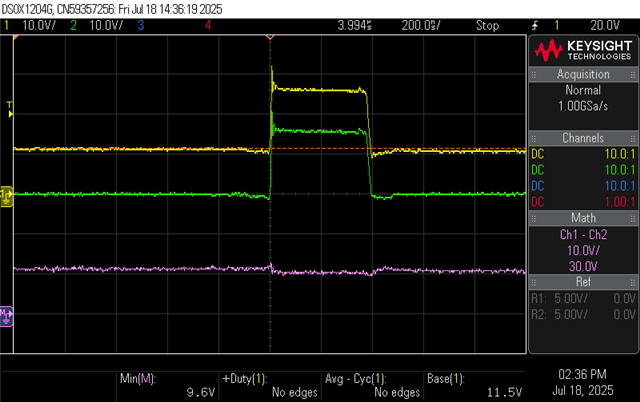

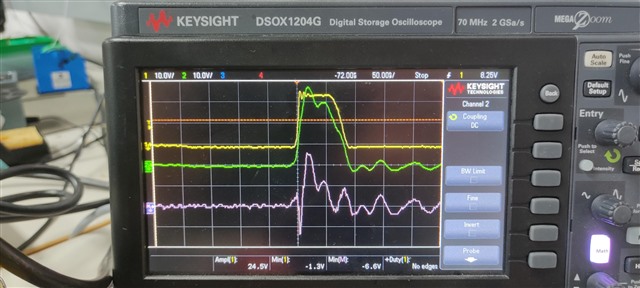

Abnormal Behavior (70ns)

- CH1 = HS - GND

- CH2 = HO - GND

- Purple = HO-HS

Right now i am suspecting 2 different possibilities:

- The UVLO of the Gate driver is turning off HO

- The HO Gate oscillations are going low enough to turn off the MOSFET and it is not turning on again afterwards (because the Bootstrap capacitor is discharged?)

What i have tested yet:

- HI and LI seem to be stable, i measured HI and LI against GND near the Gate Driver. While the length of the Pulse on HI and LI stay stable, the Pulses on HO are sporadically shorter.

- Bootstrap capacitor: I am using a 100nF Capacitor which i have soldered directly to the Pins HB and HS. Before, I had a 100nF and 1uF Capacitor in parallel on the underside of the PCB, connected with vias to the HB and HS Pins

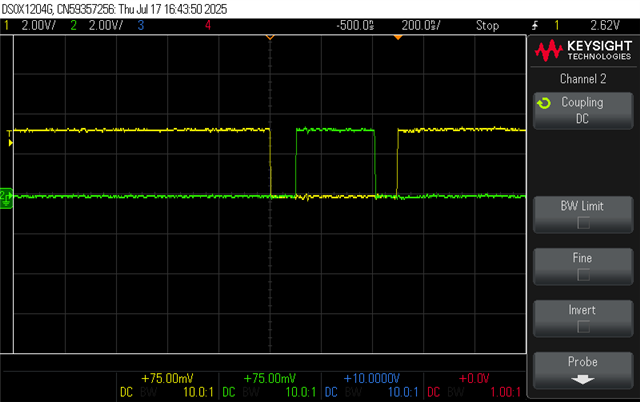

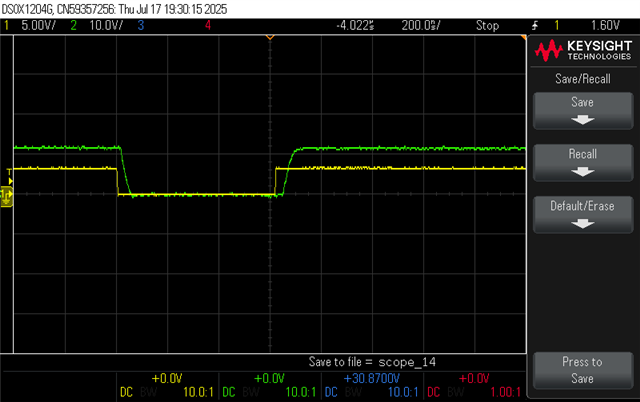

I measured the voltage on the Bootstrap capacitor. It does seem to drop lower than the UVLO threshold, but I am not sure if the UVLO is activating in this short timeframe. Somewhere else I read about a 1us delay on the UVLO.

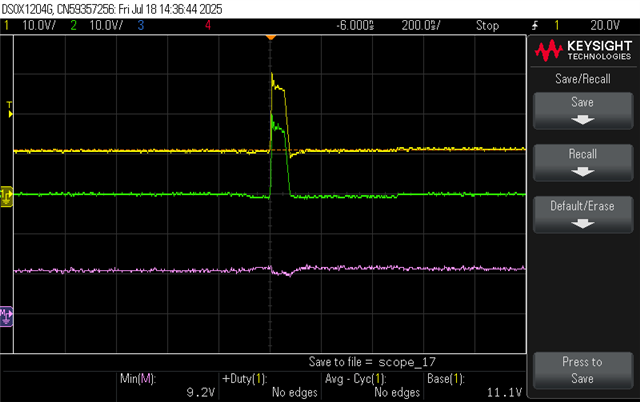

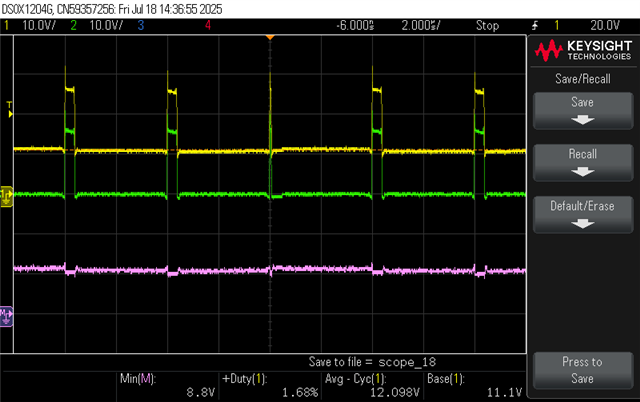

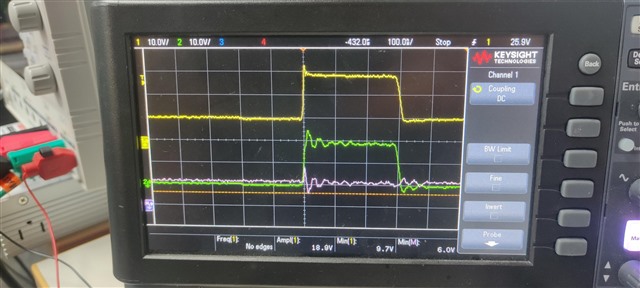

Bootstrap capacitor

- CH1 = HS - GND

- CH2 = HB - GND

- Purple = HB-HS

- VCC: I measured the voltage on the VCC capacitor. I am using a 1uF Capacitor. The Voltage on the VCC Pin seems to stay stable

- Gate Resistance: I experimented with different Gate resistors. A gate resistor higher than 5 Ohm seems to improve the behavior. From this I conclude that abnormal behavior is somehow caused by oscillations on the HS gate. The traces of HO and LO are quite long which are causing a high inductance.

In the next iteration of my design i am planning to shorten HO and LO traces as much as possible. Furthermore, the Bootstrap capacitor will be placed on the upper side next to the Gate driver and decreased to 100nF.

But I am still trying to figure out the root cause of this problem. Can this behavior be caused by the UVLO? Or are the oscillations of the Gates the cause of the Mosfet turning off.

Your help is much appreciated

Best regards

Lars Pfueller