Other Parts Discussed in Thread: TPS7B7702-Q1,

Tool/software:

Our company's preliminary PoC model is currently reviewing your company's TPS7B7701-Q1/TPS7B7702-Q1.

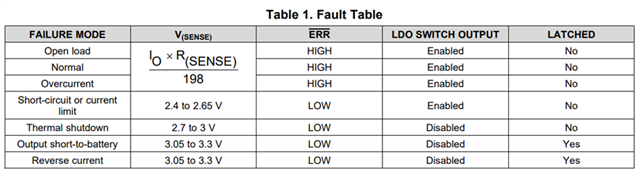

I saw the following description in the datasheet:

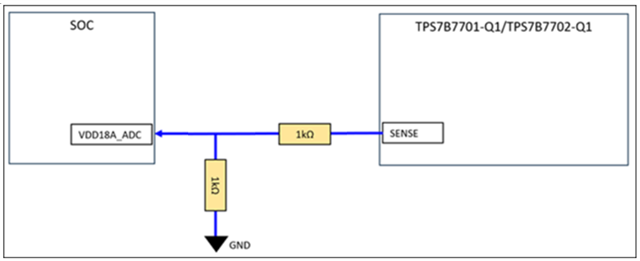

Usage scenarios:

The SENSE pin of this IC is connected to the VDD18A_ADC of the SOC,

The valid detection value (max) for this pin (VDD18A_ADC) is 1.7V~1.8V~1.9V,

The pin withstand voltage is 2.5V.

Could you please confirm the following questions:

①、When the LDO switch output is disabled, is the output of SENSE a momentary high level, or will it continue to maintain a high level? (I am concerned it could cause damage to the subsequent stage)

(in cases of short circuit, current limit, thermal shutdown, etc.)

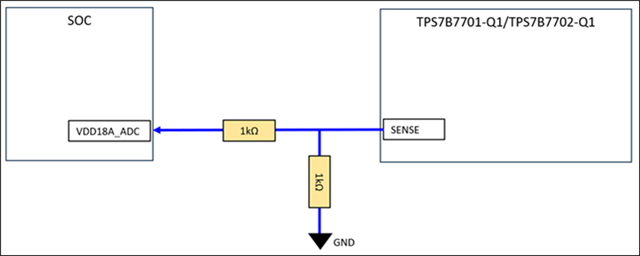

②、Is there any problem using the following circuit in the situation where issue ① occurs?

Thank you for your help.