Tool/software:

Hi Team,

We are using this DRP part in our design. Kindly review the schematic.

HD3SS3220IRNHT

1) whether this IC needs any power control switch?

2) The Vbus_det pin can be directly connected to 5V supply with 900k resistor right? is there anything to be taken care?

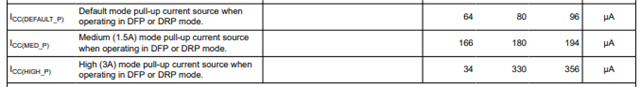

3) Current consumption of each rail - 3.3V and 5V? (VDD5 and VCC33)

Regards,

Sathya Priya N