Other Parts Discussed in Thread: UCC21750

Tool/software:

Hi team,

We got a question from customer as below.

Below is start up waveform on UCC21750. CH1=input PWM, CH2=RDY PIN, CH3=RESET PIN, CH4=VCC. There have external pull up at RDY PIN. I want to know why RDY will go high when RESET have a short low pulse, VCC just go to >2.85V.

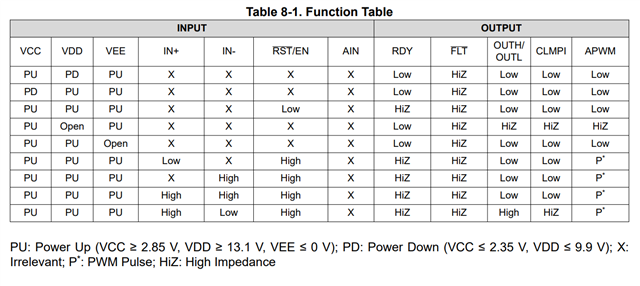

This is unknown condition which is not show in below table. In this case, VCC should be PU, VDD is PD, RESET is low, what is correct behavior for RDY PIN state?

Thanks!

Ethan Wen