Tool/software:

Hello,

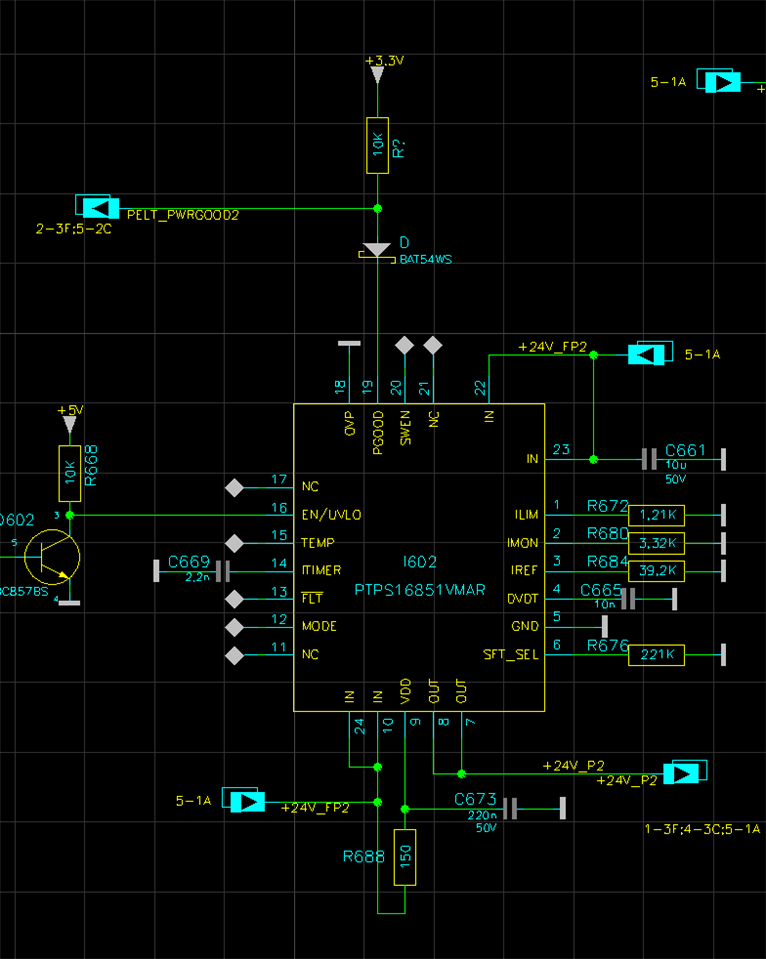

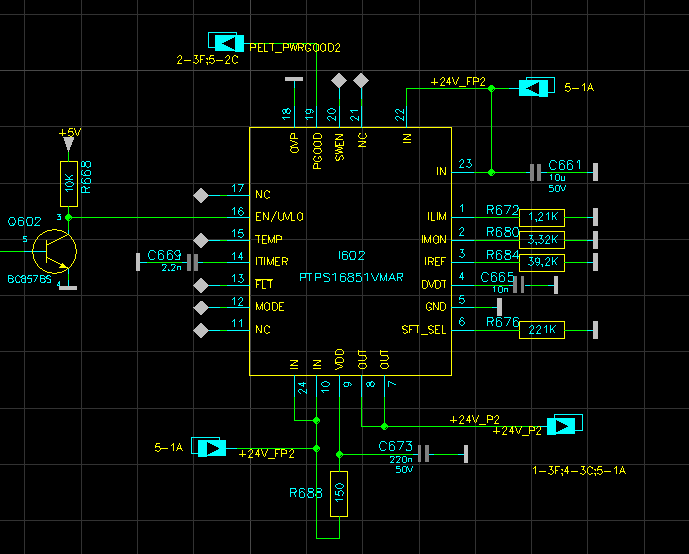

For a redesign of a current board, we use 4 TPS1685 eFuse.

Our new boards just arrived, but during the validation we see that the overcurrentprotection (with blanking timer) doesn't work.

The short circuit protection works properly, so it's only the normal overcurrent protection that doesn't seems to work properly.

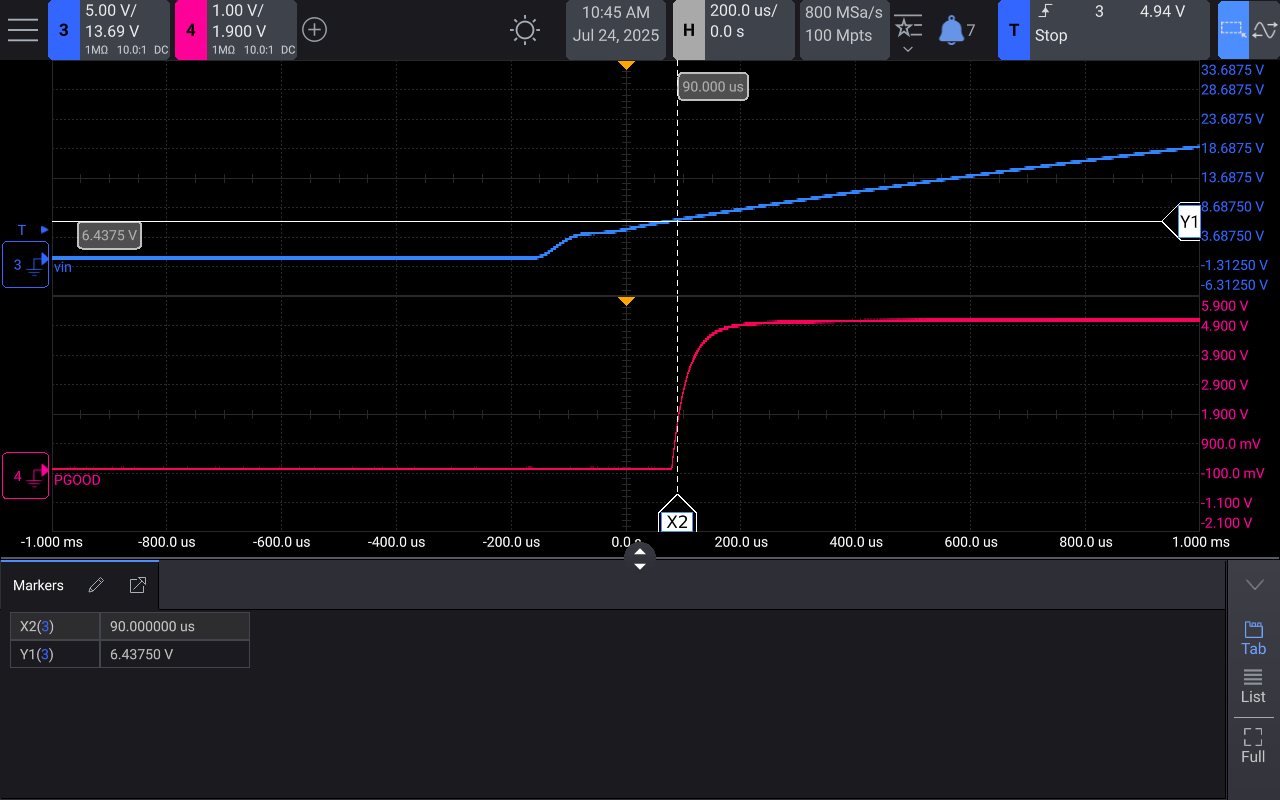

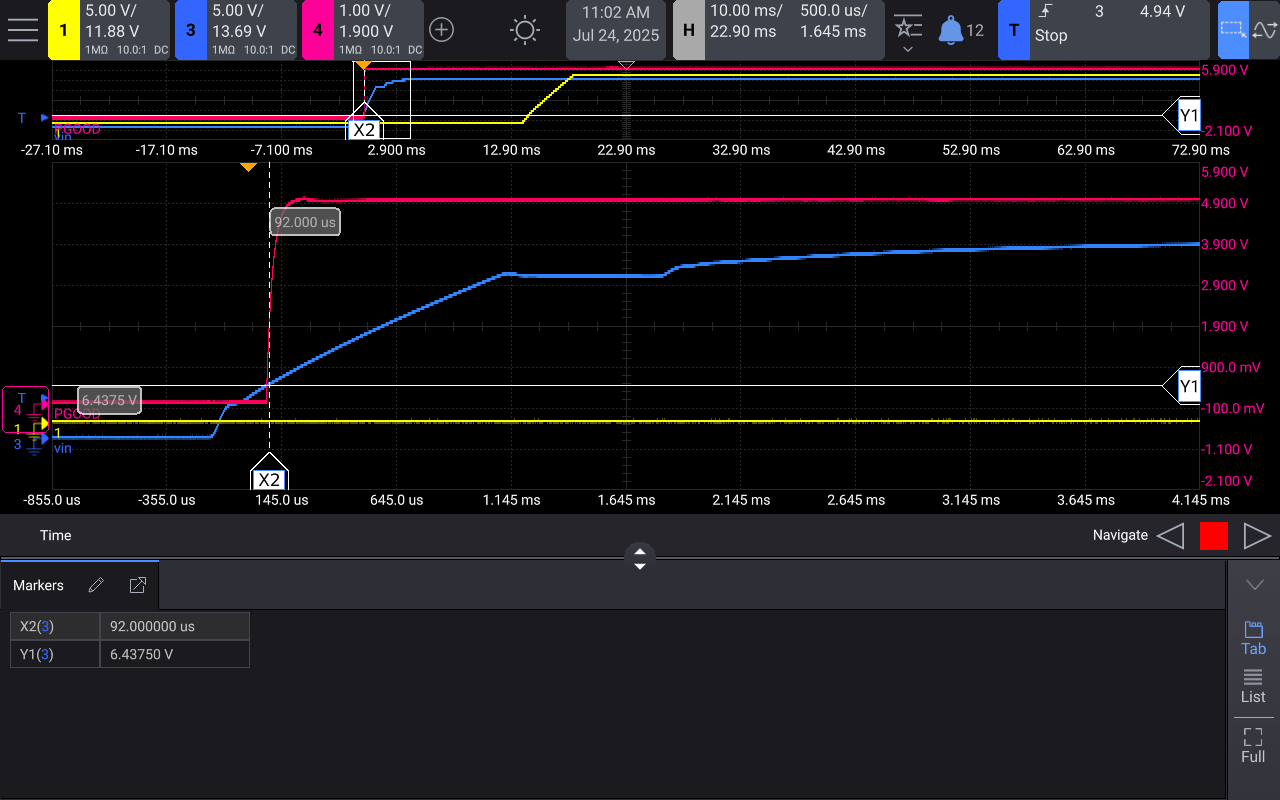

The strange thing is that the eFuse sees a overcurrent condition, when Imon becomes higher then Iref (1V).

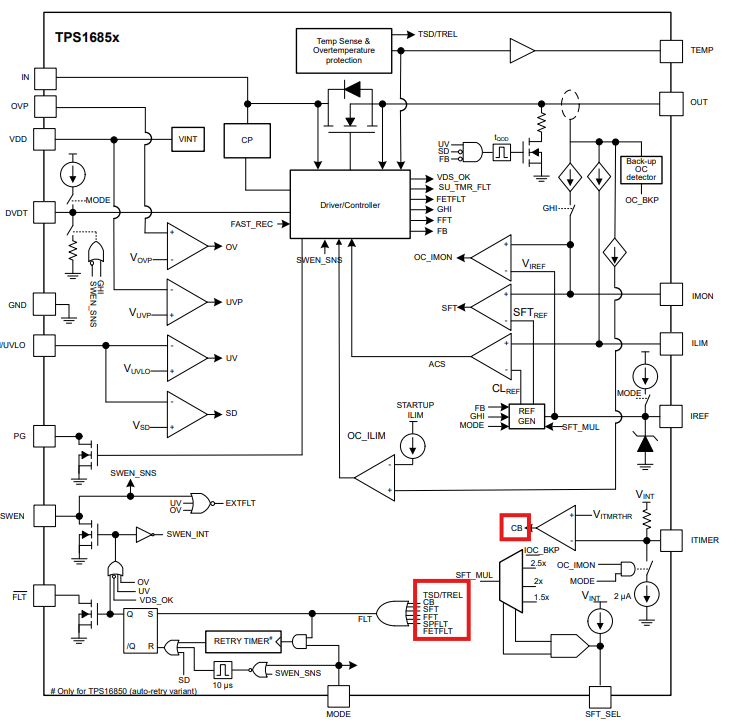

The Itimer capacitor start discharging with a constant current source, but when the voltage at Itimer is decreased with ΔVITMR the FET isn't disabled.

According to the block diagram this should also reset the internal FET, the same way as the short circuit protection.

We double check the behavior with the TPS1685EVM, with this board the overcurrent protection seems to work fine.

We even soldered the same setting capacitors and resistors to the EVM board but there the overcurrent protection seems to work properly

Kind Regards

Alexander