Tool/software:

Greetings,

I'm using BQ76972 for a 4S smart battery design, with the STM32H7 host MCU communicating with the battery monitor over I2C bus configured for 400kHz fast mode. I observed a few peculiar I2C communication features while analyzing the bus traffic, and would like to request your guidance on which of these are to be expected. Ultimately, I would like to validate my hardware design. A few notes on the latter:

- Host MCU I2C peripheral is configured to 400kHz master mode, clock stretching enabled

- Host MCU communicates with the battery monitor over a pair of LTC4331 differential extenders, with the total bus spanning multiple PCBs. Notably, the link rate on both the local and remote LTC4331 extenders are configured to 500kHz. See the bus visualized below:

[MCU] <-I2C 400k, 2k2 pullups-> [local LTC4331] <-twisted differential pair-> [remote LTC4331] <-I2C 400k, 2k7 pullups-> [BQ76972]

All oscilliscope/logic analyzer captures attached below were taken on the segment in bold.

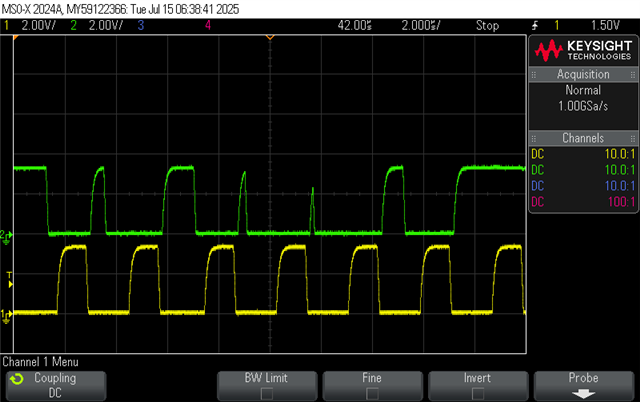

(1) SDA glitches

While the communication appears to be working correctly, my scope/logic analyzer are showing unusual "glitches" on the SDA line. These glitches are very short pulses that occur between the SCL clock pulses, specifically when the SCL line is low. SDA signal appears to be stable during the rising edge of SCL and these glitches appear to not occur when SCL is high.

Question: are the glitches expected and harmless?

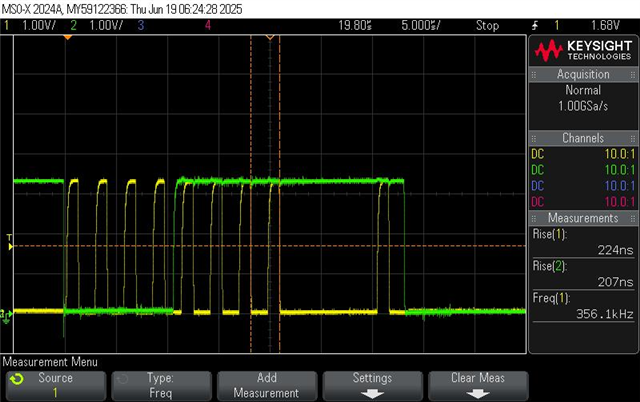

(2) Lower than expected clock frequency

I consistently measured the SCL frequency to be ~355kHz, which is lower than the expected 400kHz. The datasheet doesn't clearly specify the expected frequency tolerance. As mentioned above, the differential I2C link is configured to 500kHz, while host MCU to 400kHz, suggesting they are not the bottleneck.

Question: is it expected that the actual BQ76972 SCL frequency is 355kHz when the device is configured in 400kHz I2C fast mode? If not, would you suspect the lower frequency to be caused by the host/diff I2C link?

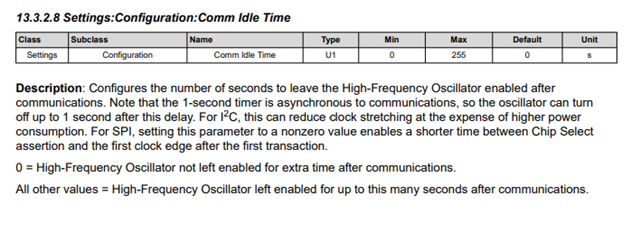

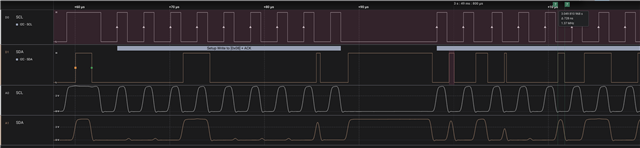

(3) Excessive clock stretching

I am observing significant clock stretching when communicating with BQ76972 over I2C at 400kHz, which is substantially impacting my bus throughput. As shown in the attached logic analyzer capture, the device holds the SCL line low between bytes for periods that are often longer than the time it takes to transmit an entire byte, effectively doubling the transmission time.

Question: Is this aggressive clock stretching considered normal operating behavior for the BQ76972, or could it indicate an issue with my setup?

Thank you in advance for your time and support.

Kind regards,

Vasily