Other Parts Discussed in Thread: UCC27624, UCC57108

Tool/software:

Hi,

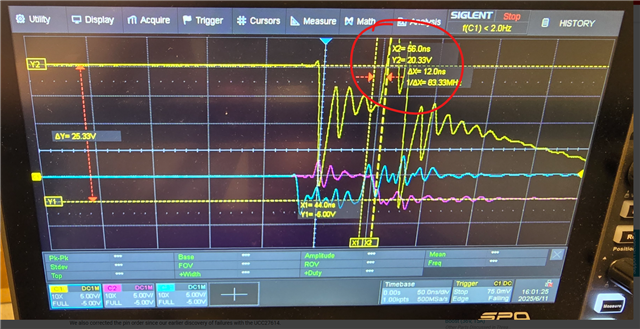

Following up on the previous discussion in this forum—we initially believed we had found a workaround for this issue. However, we've now observed that during switching events around 2000A at ~1000V, our current design occasionally triggers a brief glitch on the gate driver's input signal. This glitch, likely occurring within the same critical timing window as previously discussed, appears to cause permanent damage to the driver. The failure mode is identical to what we’ve seen before: no short on the OUT pins, but the driver stops functioning as if some internal logic or level shifter has been compromised.

Could you please confirm whether this issue has been addressed in upcoming batches? If not, we may need to explore alternative solutions and would welcome any recommendations.

Thanks in advance.