Other Parts Discussed in Thread: TPS628503, TPS628303, TPS628513

Tool/software:

Dear TI Forum,

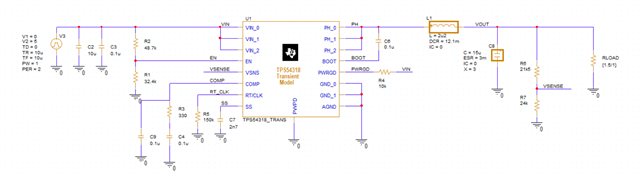

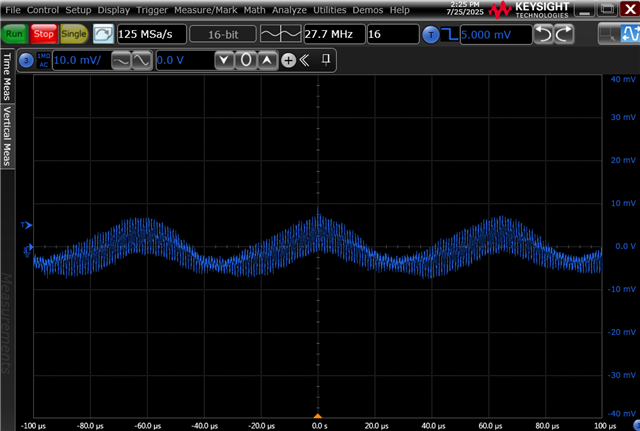

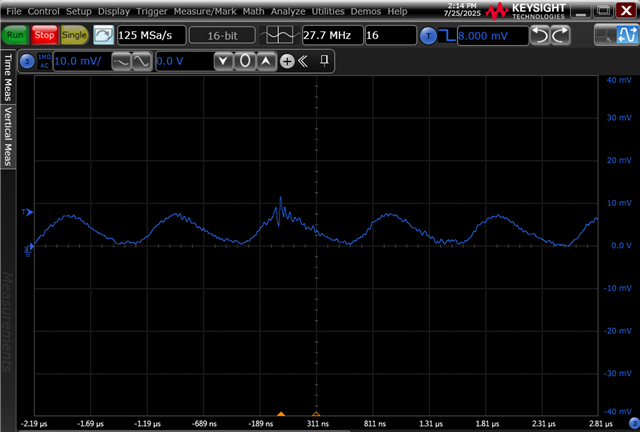

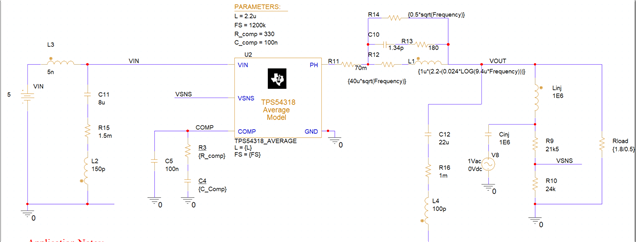

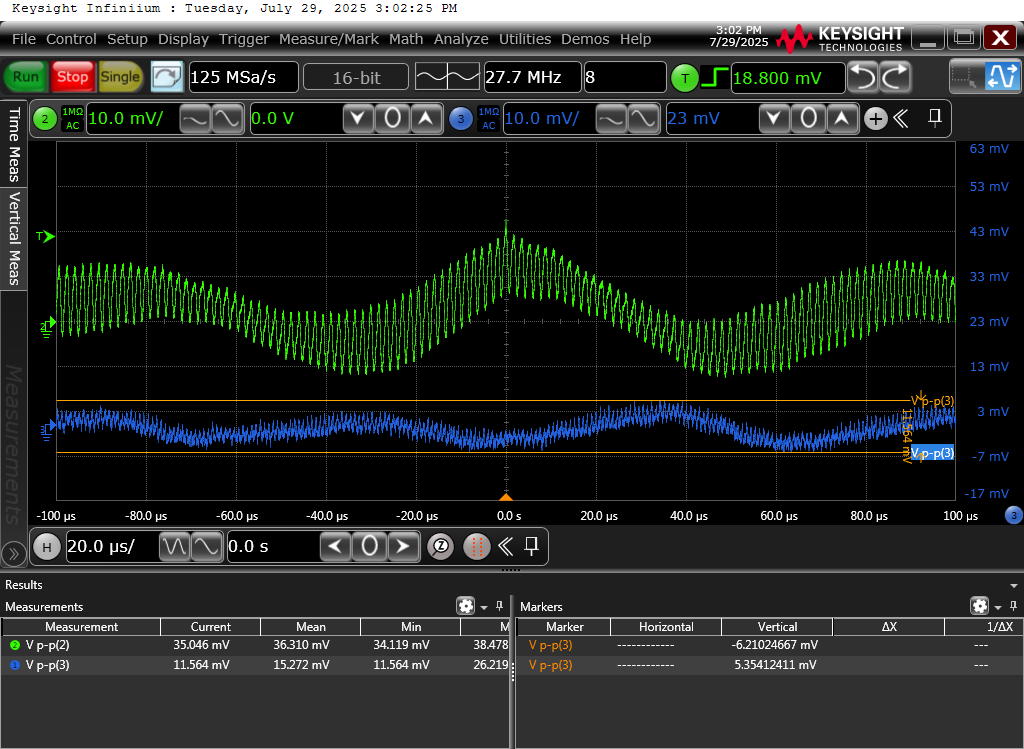

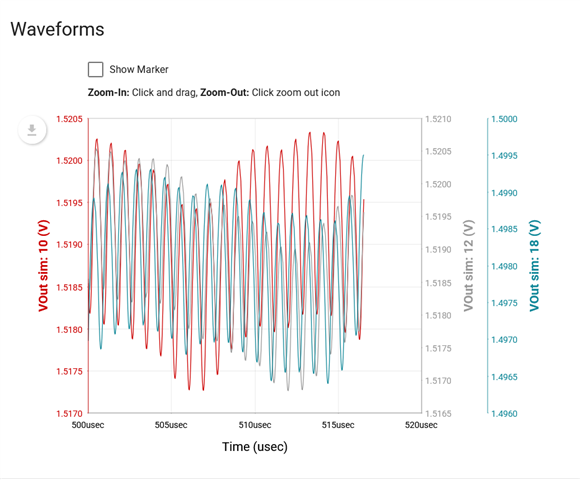

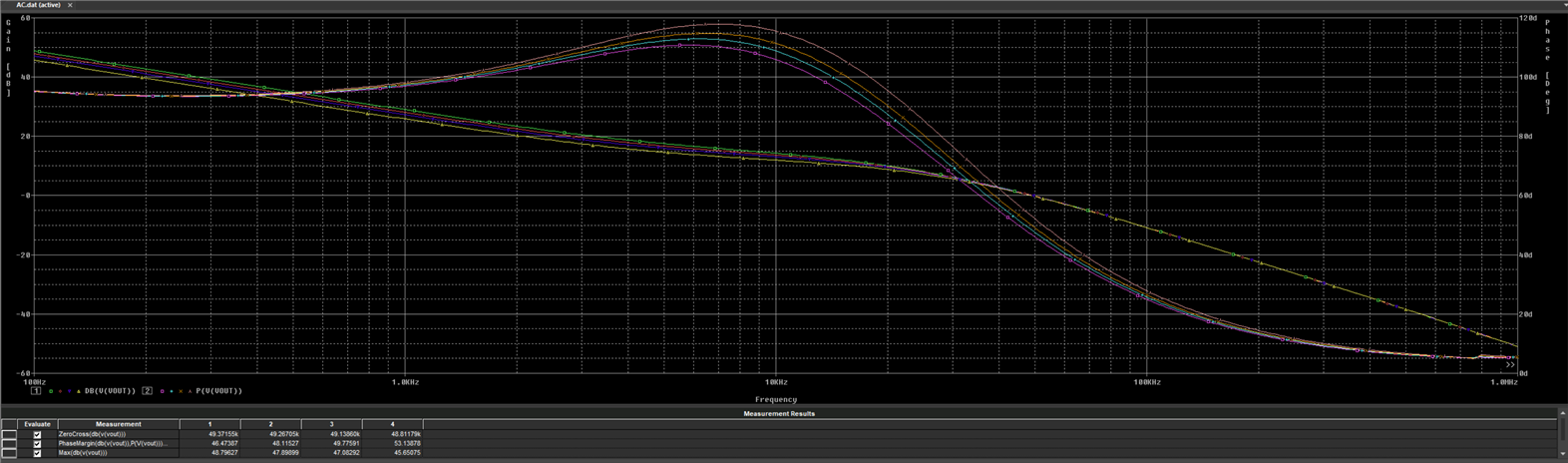

I've measured the output voltage ripple of the TPS54318. Besides the switching noise of around 8mV_pp there is a beat frequency of around 12 kHz which increases the overall output voltage deviation to 16mV_pp.

Is this due to the internal voltage regulation?

Thank you.

Kind regards

Moritz