Tool/software:

Hi support team all.

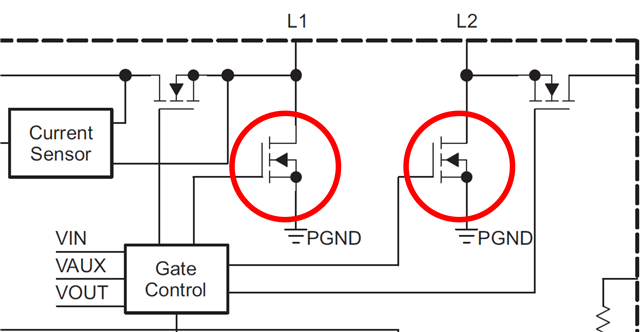

Switching behavior

Is it possible for both internal FETs in the diagram below to be turned on at the same time?

If so, under what conditions does this occur?

Currently, it has been confirmed that two FETs are turned on at the same time, which wastes energy in the inductor and prevents the output voltage from rising to the set voltage.

Best regards,

DH