Tool/software:

Hi TI Team,

We are using the PD controller where we require a 12V (Min/Max) input with a 3A supply current.

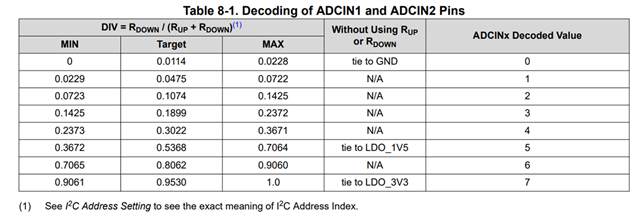

As per the datasheet, we have calculated the resistor divider values based on the ADCINx decoded value table (Table 8.1), which is attached below for your reference.

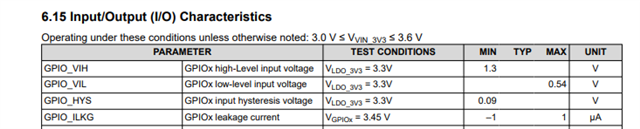

Could you please review the configuration and confirm if it meets the requirements for 12V@3A operation and FALUT_IN pin can be directly connected to the processor GPIO?

Please let us know if any additional information is needed.

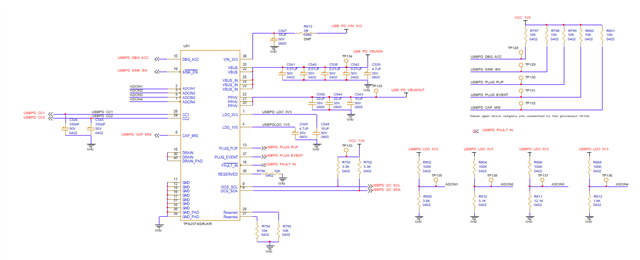

Additionally, I have attached the schematic for review.

Thanks & Regards,

Jaydip

| 12V 3A input | Pulled up at 3.3V | ADC decoded value | ||

| ADC Input voltage | Rbottom | Rtop | ||

| ADCIN1 | 0.114671815 | 3.6K | 100K | 2 |

| ADCIN2 | 0.160133206 | 5.1K | 100K | 3 |

| ADCIN3 | 0.356199822 | 12.1K | 100K | 3 |

| ADCIN4 | 0.058349705 | 1.8K | 100K | 1 |